Hardware Reference

In-Depth Information

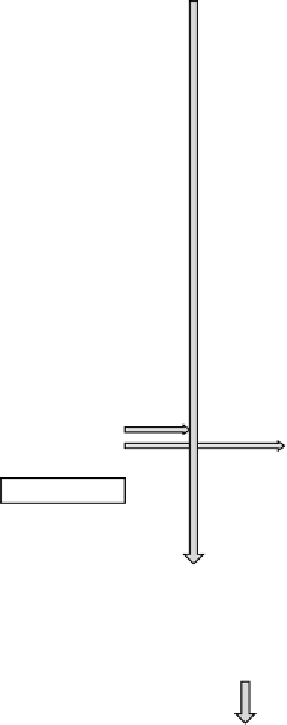

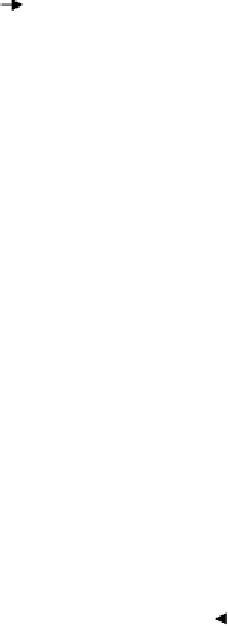

Memory

control

registers

MAR

To

and

from

main

memory

MDR

PC

Instruction

fetch unit

(IFU)

MBR1

MBR2

SP

LV

Control signals

CPP

Enable onto B bus

TOS

Write C bus to register

OPC

Cbus

Bbus

H

Abus

C latch

A latch

B latch

6

ALU

control

N

ALU

Z

Shifter

Figure 4-31.

The three-bus data path used in the Mic-3.

registers, we will continue to assume that a memory operation takes one cycle. In

practice, though, this may not be so easy to achieve.

The second point deals with throughput rather than the speed of an individual

instruction. In the Mic-2, during the first and third parts of each clock cycle the

ALU is idle. By breaking the data path up into three pieces, we will be able to use

the ALU on every cycle, getting three times as much work out of the machine.