Hardware Reference

In-Depth Information

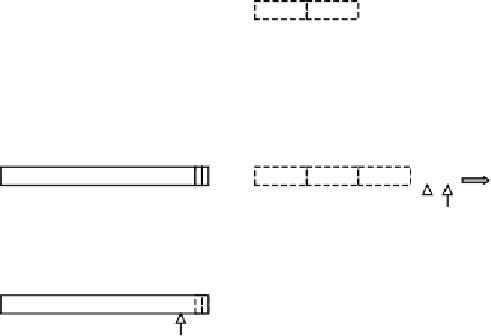

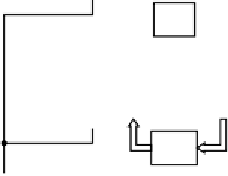

MBR2

Shift register

From memory

IMAR

MBR1

+1

2 low-order bits

Cbus

Bbus

PC

+1, 2

Write PC

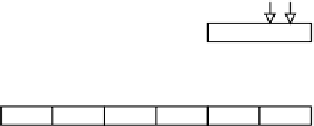

Figure 4-27.

A fetch unit for the Mic-1.

We show the rudiments of the second scheme in Fig. 4-27. Rather than a single

8-bit

MBR

, there are now two

MBR

s: the 8-bit

MBR1

and the 16-bit

MBR2

. The IFU

keeps track of the most recent byte or bytes consumed by the main execution unit.

It also makes available in

MBR1

the next byte, just as in the Mic-1, except that it

automatically senses when the

MBR1

is read, prefetches the next byte, and loads it

into

MBR1

immediately. As in the Mic-1, it has two interfaces to the B bus:

MBR1

and

MBR1U

. The former is sign-extended to 32 bits; the latter is zero-extended.

Similarly,

MBR2

provides the same functionality but holds the next 2 bytes. It

also has two interfaces to the B bus:

MBR2

and

MBR2U

, gating the 32-bit sign-ex-

tended and zero-extended values, respectively.

The IFU is responsible for fetching a stream of bytes. It does this by using a

conventional 4-byte memory port, fetching entire 4-byte words ahead of time and

loading the consecutive bytes into a shift register that supplies them one or two at a

time, in the order fetched. The function of the shift register is to maintain a queue

of bytes from memory, to feed

MBR1

and

MBR2

.

At all times,

MBR1

holds the oldest byte in the shift register and

MBR2

holds

the oldest 2 bytes (oldest byte on the left), forming a 16-bit integer [see

Fig. 4-19(b)]. The 2 bytes in

MBR2

may be from different memory words, because

IJVM instructions do not align on word boundaries in memory.

Whenever

MBR1

is read, the shift register shifts right 1 byte. Whenever

MBR2

is read, it shifts right 2 bytes. Then

MBR1

and

MBR2

are reloaded from the oldest

byte and pair of bytes, respectively. If there is sufficient room now left in the shift

register for another whole word, the IFU starts a memory cycle in order to read it.