Hardware Reference

In-Depth Information

it needs to, it then asserts a special signal that we will call

MSYN

(Master SYN-

chronization). When the

slave

sees this, it performs the work as fast as it can.

When it is done, it asserts

SSYN

(Slave SYNchronization).

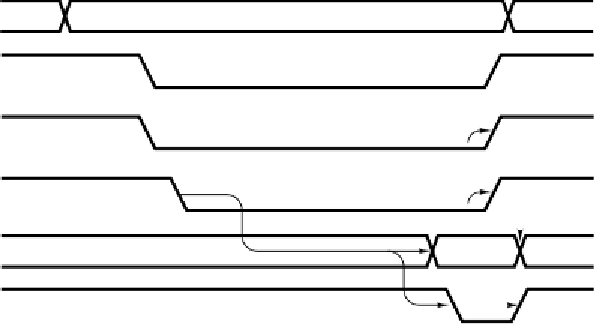

ADDRESS

Memory address to be read

MREQ

RD

MSYN

Data

DATA

SSYN

Figure 3-39.

Operation of an asynchronous bus.

As soon as the master sees

SSYN

asserted, it knows that the da

ta are

a

vai

lable,

so it l

atches them and then negates the ad

dress l

ines, along with

MREQ

,

RD

, and

MSYN

. When the slave s

ees the

negation of

MSYN

, it knows that the cycle has been

completed, so it negates

SSYN

, and we are back in the original situation, with all

signals negated, waiting for the next master.

Timing diagrams of asynchronous buses (and sometimes synchronous bu

ses as

well) use arrows to show cause and effect, as in Fig. 3-39. The asserti

on of

MSYN

causes the d

ata li

nes to be asserted and also causes the slave to as

sert

SS

Y

N

.

The

asserti

on of

SSYN

, in turn, caus

es the

negation of the address

lines

,

MREQ

,

RD

, and

MSYN

. Finally, the negation of

MSYN

causes the negation of

SSYN

, which ends the

read and returns the system to its original state.

A set of signals that interlocks this way is called a

full handshake

. The essen-

tial part consists of four events:

1.

MSYN

is asserted.

2.

SSYN

is asserted in response to

MSYN

.

3.

MSYN

is negated in response to

SSYN

.

4.

SSYN

is negated in response to the negation of

MSYN

.

It should be clear that full handshakes are timing independent. Each event is

caused by a prior event, not by a clock pulse. If a particular master/slave pair is

slow, that in no way affects a subsequent master/slave pair that is much faster.