Hardware Reference

In-Depth Information

d

Δ

a

b

b AND c

d

c

c

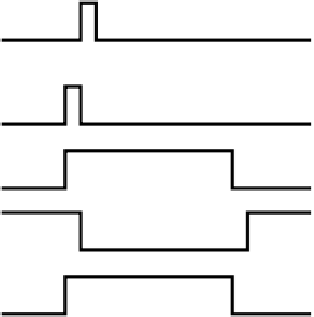

(a)

b

a

Time

(b)

Figure 3-24.

(a) A pulse generator. (b) Timing at four points in the circuit.

Fig. 3-24(b). This time shifting just means that the D latch will be activated at a

fixed delay after the rising edge of the clock, but it has no effect on the pulse

width. In a memory with a 10-nsec cycle time, a 1-nsec pulse telling it when to

sample the

D

line may be short enough, in which case the full circuit can be that of

Fig. 3-25. It is worth noting that this flip-flop design is nice because it is easy to

understand, but in practice more sophisticated flip-flops are normally used.

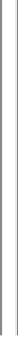

D

Q

Q

Figure 3-25.

A D flip-flop.

The standard symbols for latches and flip-flops are shown in Fig. 3-26. Figure

3-26(a) is a latch whose state is loaded when the clock,

CK

, is 1. It is in contrast to

Fig. 3-26(b) which is a latch whose clock is normally 1 but which drops to 0