Digital Signal Processing Reference

In-Depth Information

C

1

C

4

4

H

1

D

IN

/H

2

SR/H

0

EC

Register

Bypass

S/R

Control

G

4

G

3

G

2

G

1

YQ

SD

LookUp

Table

(LUT)

D

Q

Programmable

Register

EC

RD

LookUp

Table

(LUT)

1

Y

Register

Bypass

S/R

Control

XQ

SD

F

4

F

3

F

2

F

1

D

Q

LookUp

Table

(LUT)

EC

Programmable

Register

RD

1

K

(Clock)

X

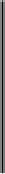

Figure 3.12

Xilinx 4000 Family Configurable Logic Block (CLB).

CLBs are arranged in a square matrix with a programmable hierarchical

interconnection network. Devices in the family contain from 100 to 3,136

CLBs. The multiplexers seen in Figure 3.12 are all controlled by bits in the

FPGA's SRAM configuration memory.

The complex hierarchical interconnection network contains varying length

row, column, and neighboring CLB interconnect structures. Eight low-skew

global clock buffers are also provided. Input-output blocks (IOBs), contain

programmable tri-state drivers and optional registers. Each I/O pin can be

programmed as input, output, output with a tri-state driver, or tri-state bi-

directional with or without a register. In the more recent Xilinx Virtex 4

FPGAs, each CLB now contains four circuits similar to the earlier 4000 CLBs.

3.5 Computer Aided Design Tools for Programmable Logic

Increasing design complexity and higher gate densities are forcing digital

designs to undergo a paradigm shift. Old technology, low-density logic

families, such as the TTL 7400 or simple PLD families are rarely if ever used in

new designs. With logic capacities of an individual FPGA chip approaching

10,000,000 gates, manual design at the gate level is no longer a viable option in

complex systems. Rapid prototyping using hardware description languages

(HDLs), IP cores, and logic synthesis tools has all but replaced traditional gate-

level design with schematic capture entry. These new HDL-based logic

synthesis tools can be used for both ASIC and FPGA-based designs. The two

most widely used HDLs at the present time are VHDL and Verilog.