Digital Signal Processing Reference

In-Depth Information

The testbench approach is critical in large ASIC designs where all errors are

costly. Automatic Test Equipment (ATE) can also use a properly written

testbench and its test vector and timing information to physically test each

ASIC chip for correct operation after production. In large designs, the testbench

can require as much time and effort as the UUT's synthesis model. By

performing both a functional simulation and a timing simulation of the UUT

with the same test vectors, it is also possible to check for any synthesis-related

errors.

6.17 For additional information

The chapter has introduced the basics of using VHDL for digital synthesis. It

has not explored all of the language options available. The Altera online help

contains VHDL syntax and templates. A large number of VHDL reference

textbooks are also available. Unfortunately, only a few of them currently

examine using VHDL models that can be used for digital logic synthesis. One

such text is

HDL Chip Design

by Douglas J. Smith, Doone Publications, 1996.

A number of alternative integer multiply, divide, and floating-point algorithms

with different speed versus area tradeoffs can be found in computer arithmetic

textbooks. Two such examples are

Digital Computer Arithmetic Design and

Implementation

by Cavanagh, McGraw Hill, 1984, and

Computer Arithmetic

Algorithms

by Israel Koren, Prentice Hall, 1993.

6.18 Laboratory Exercises

1.

Rewrite and compile the VHDL model for the seven-segment decoder in Section 6.5

replacing the PROCESS and CASE statements with a WITH…SELECT statement.

2.

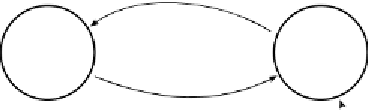

Write a VHDL model for the state machine shown in the following state diagram and

verify correct operation with a simulation using the Altera CAD tools. A and B are the

two states, X is the output, and Y is the input. Use the timing analyzer to determine the

maximum clock frequency on the Cyclone EP1C6Q240C8 device.

1

1

A

X = 0

B

X= 1

0

0

Reset

3.

Write a VHDL model for a 32-bit, arithmetic logic unit (ALU). Verify correct operation

with a simulation using the Altera CAD tools. A and B are 32-bit inputs to the ALU, and

Y is the output. A shift operation follows the arithmetic and logical operation. The

opcode controls ALU functions as follows: