Hardware Reference

In-Depth Information

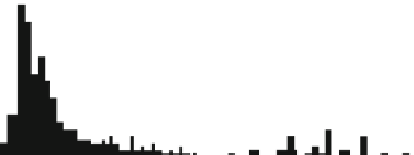

% OF SAMPLES

in fabrication lot

I

DDQ

Test Threshold

I

DDQ

1 nA

10 nA

100 nA

1 uA

10 uA

100 uA

1 mA

NON DEFECTIVE

DEFECTIVE

Fig. 2.15

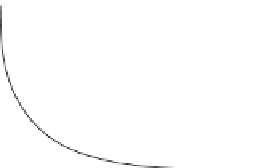

100

1

0.2

0.3

Gate lengh (µm)

be considered nominal anymore but ranging within a statistical distribution (

Ferre

and Figueras

2002

). Assuming also a statistical distribution for defective devices,

only a clear distinction between defect-free and defective devices could be made

if both distributions are far enough. However, this is far from reality as shown in

Fig.

2.15

where the histogram of the current consumption for a real fabricated lot of

circuits illustrates the fact that the defect-free circuits consumption overlap the de-

fective circuits consumption (

Figueras and Ferre

1998

). Indeed, the leakage current

increases in an exponential way for every new CMOS technology node, as described

current mean value of the distribution of the fault-free devices increases and gets

closer to the mean of the defective devices, overlapping both distributions. Thereby,

it becomes more difficult to determine whether a variation in the I

DDQ

value is due

to the leakage current or due to a defect.

2.3.3.2

Other Quiescent Current Testing Techniques

Some techniques based on the post-processing of I

DDQ

data have been developed

to extend the effectiveness of I

DDQ

. One of these techniques is the so-called 'Delta