Information Technology Reference

In-Depth Information

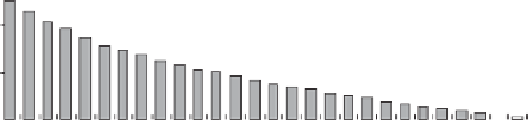

With the 2D pyramidal model, we can estimate the maximum number of

connections for each metal layer. Assuming a square core with size of 0.0004mm

2

,

we use the parameters from The International Technology Roadmap for Semi-

conductors (ITRS) in 2006 [78]. For simplicity, we will also assume that window-

to-window spacings are equal, even between layers, and the required spacing of

the windows from the edges of the core is zero. According to the Technology

Roadmap, the highest metal layer we could have in 2006 is metal 11. However, in

order to demonstrate the relationship of the number of connections to the number

of metal layers, we increase metal layers up to a maximum of 29 layers. We

illustrate the possible connections for each metal layer in Figure 17.11.

As you can see in Figure 17.11, the number of connections for each layer

decreases as the metal layers increase since the window size becomes larger and the

remaining space for windows on each higher layer becomes smaller. Therefore,

given a core area, we can determine how many more connections we can get as we

add more metal layers with the 2D pyramidal model.

The utility of the flip-chip technology to enhance interconnection is decreased

as the number of available metal layers increases. In order to demonstrate our

model, we utilize Direct Bond Interconnect (DBI) [82] as an example. The

Ziptronix DBI technology enables silicon and other technologies to be bonded

and interconnected in a 3D fashion. It achieves high-density vertical interconnec-

tions without any volume exclusions (i.e., without ''wasted space'' for the

interconnect) in the CMOS device. It supports an interconnect pitch of less than

10 microns, with typical interconnect width of 2

lm

m and alignment accuracy of

1

lm

m.

For our analysis, we choose the pitch of the vertical window to be 1

l m

. At this

point, other parameters are unchanged. Figure 17.12 shows that the total outgoing

number of connections to the core increases but the number of vertical inter-

connections between chips will decrease due to less availability of vertical

connection area as we have more layers to connect horizontally (on the die) to

the core.

Given the same core area, Figure 17.13 compares the number of connections

of a side of a flip-chip design with that of a conventional 2D design. DBI

600

400

200

0

1

3579 1 3 5

Metal Layer

17

19

21

23

25

27

29

Figure

17.11.

Number of connections as a function of available metal layers.

Search WWH ::

Custom Search