Hardware Reference

In-Depth Information

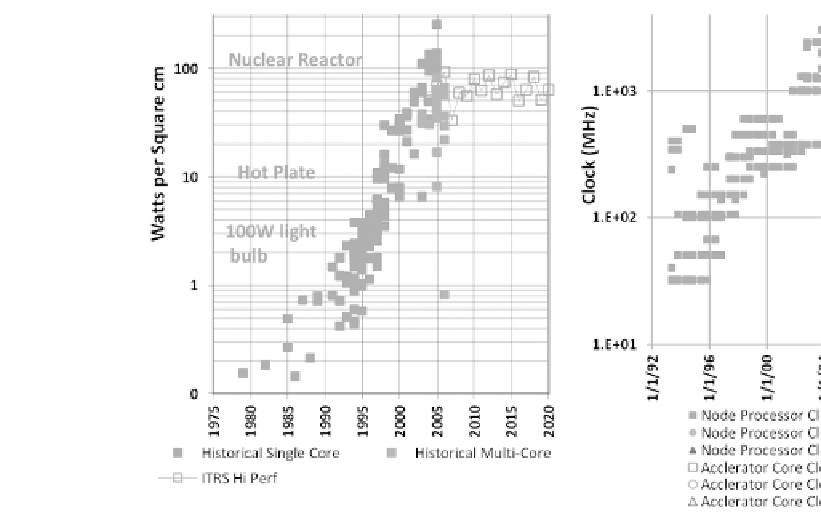

FIGURE 29.2: The Power and Clock Inflection point in 2004. Unable to con-

tinue reductions in supply voltages, we saw a nearly exponential rise in chip

thermal density|approaching that of a nuclear reactor by 2004. To avoid

melting the chip, the industry was forced to abandon historical increases in

clock frequency. By 2008, the trends in clock frequency growth across the in-

dustry had leveled off when chips reached their thermal density limits, which

leads to exponential rise in parallelism to continue historical performance im-

provements.

consistency semantics and current approaches to maintaining reliability of

storage systems. The challenges to I/O system design that are posed by this

exponential rise in parallelism will be treated in more detail in Chapter 31.

29.1.3 Toward Data-Centric Computing (2014{2022)

Since the loss of Dennard Scaling, a new technology-scaling regime has

emerged. Due to the laws of electrical resistance and capacitance, the intrinsic

energy eciency for a fixed-length wire does not improve appreciably as it

shrinks down with Moore's law improvements in lithography, as shown in

Figure 29.1. In contrast, the power consumption of transistors continues to

decrease as their gate size (and hence capacitance) decreases. Since the energy

eciency of transistors is improving as their sizes shrink, and the energy

eciency of wires is not improving, the point is rapidly approaching where