Hardware Reference

In-Depth Information

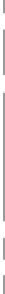

+V

DD

M

17

M

13

M

9

M

20

M

21

M

19

M

10

M

14

M

22

M

23

M

5

M

1

M

3

M

7

50uA

Z

Y

X

M

8

M

6

M

4

M

2

M

11

M

28

M

15

M

26

M

24

M

12

M

27

M

25

M

18

M

16

−V

SS

Fig. 4.7 Class-AB CCII+ realization proposed by Calvo et al. (Adapted from [

43

]

2003

©

Springer)

The simulation results using 0.8

ʼ

m CMOS technology of this CC with

3.3 V

power supplies show that the resistance at X-terminal is 42

Ω

, and impedance at

Y-terminal is 174 k

Ω

||1.23 pF while the Z-terminal parasitic output impedance

consists of 2.24 M

||0.21 pF. A very low input offset voltage of value 0.2 mV and

input offset current of 50.2 nA are achievable.

Ω

4.8 CMOS-Inverter-Based CCII

Barthelemy et al. [

51

] presented a CCII+ implementation based upon classical

CMOS inverters operating in transconductance mode. The aspect ratios of the

NMOS and PMOS transistors are assumed to be set such that a voltage transition

is obtained around V

IN

¼

V

OUT

¼

V

DD

/2. This condition leads to a common-mode

voltage V

CM

¼

V

DD

/2. Around this voltage, the inverter exhibits a transconductance

mode between the input voltage V

in

and the output current i

out

. In the transcon-

ductance mode of operation, the small signal output current of the inverter is given

by i

out

¼

g

mN+

g

mP

, where g

mN

and g

mP

are the

NMOS and PMOS transconductance in saturated mode of operation. The proposed

CCII+ topology based upon six such inverters is shown in Fig.

4.8b

. By routine

analysis of this circuit, assuming load R

L

to be connected at node X, the expression

of V

X

in terms of V

Y

turns out to be:

g

m

v

in

(see Fig.

4.8a

), where g

m

¼

g

m

R

L

V

X

¼

g

m

R

L

V

Y

for

g

m

1

¼

g

m

2

and

g

m

3

¼

g

m

4

¼

g

m

ð

4

:

5

Þ

1

þ

Search WWH ::

Custom Search