Hardware Reference

In-Depth Information

z

+

z

−

I

1

I

2

DDCC

V

1

y

1

y

2

V

2

y

3

x

R

1

x

y

1

y

3

R

2

z+

C

DDCC

y

2

z

−

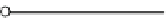

Fig. 14.12 FI with improved low frequency performance proposed by Yuce and Minaei (Adapted

from [

31

]

©

2009 Elsevier)

frequency performance. However, the structure has the drawback of requiring a

matching condition (R

1

¼

R

2

) to simulate a lossless FI.

The equivalent circuit of Fig.

14.12

with parasitic impedances is shown in

Fig.

14.13

, where L

eq

and R

eq

are given by the following expressions:

R

x

1

þ

L

eq

¼

C

þ

C

y

21

þ

C

y

23

ð

R

1

Þ

ð

R

x

2

þ

R

2

Þ

ð

14

:

20

Þ

1

R

eq

¼

ð

R

x

1

þ

R

1

Þ

ð

R

x

2

þ

R

2

Þ

=

ð

R

1

þ

R

x

1

Þ

1

=

ð

R

1

þ

R

x

1

Þ

R

y

21

R

y

23

þ

1

=

ð

14

:

21

Þ

R

eq

can be made zero if we select:

=

R

y

21

R

y

23

=

ð

R

1

þ

R

x

1

Þ

¼

=

ð

R

2

þ

R

x

2

Þ

ð

:

Þ

1

1

1

14

22

On the other hand, if we choose:

=

R

y

21

R

y

23

1

=

ð

R

1

þ

R

x

1

Þ

1

=

ð

R

2

þ

R

x

2

Þ

1

ð

14

:

23

Þ

this will ensure the stability of the circuit operation.

The authors of [

31

] have proposed as many as eight different topologies of FIs,

however, five of them require five CCs of various types while only three configu-

ration therein were implemented with only two CCs and the circuit of Fig.

14.12

is

one of these. For a rigorous analysis of all the FI circuits and their detailed SPICE

simulation results based upon a DDCC implemented with 0.35

μ

m TSMC CMOS

technology parameters, the readers are referred to [

31

].

Search WWH ::

Custom Search