Hardware Reference

In-Depth Information

a

b

y

1

x

1

y

x

DO-CCII

z

DO-CCII

z

+

z

−

R

x

y

Z

ina

Z

inb

DO-CCII

z

2

2

y

x

y x

DO-CCII

z

DO-CCII

z

Z

L

Z

L

z

+

−

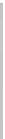

Fig. 14.11 Compensated NICs proposed by Yuce [

25

]

AD844 (which contains a CCII + and unity gain voltage buffer). If the Y and Z

terminal parasitic impedances are ignored, the input impedance looking into the

input terminals of the circuit of Fig.

14.11a

is obtained as:

Z

x

1

ʱ

01

ʲ

01

ʲ

02

ʳ

02

ðÞ

ʱ

01

ʲ

01

ʲ

02

ʳ

02

Z

ina

s

ðÞ

¼

Z

x

2

s

Z

L

s

ðÞ

ð

14

:

18

Þ

In the circuit of Fig.

14.11b

, if only X-terminal parasitic effects of the DO-CCII are

considered, the expression for its input impedance can be obtained as:

Z

inb

s

ðÞ

¼

R

x

1

þ

R

x

2

R

x

3

R

Z

L

s

ðÞ

ð

14

:

19

Þ

Thus, if we select (

R

x

1

+

R

x

2

R

x

3

)

¼

R

, the input impedance of the proposed NIC in

Fig.

14.11b

becomes

Z

inb

(

s

)¼

Z

L

(

s

) and a perfect compensation is achieved. For

detailed SPICE simulation results of this circuit, the reader is referred to [

25

].

14.11 DDCC-Based FI with Improved Low Frequency

Performance

Although a lossless FI can be realized by using two DVCCs with only three passive

elements (two resistors and a grounded capacitor), Yuce and Minaei [

31

] presented

a lossless FI structure using exactly the same number of active and passive

components but with the advantageous features of (i) accommodating the effect

of finite input resistance R

x

of both the DDCCs and (ii) ensuring that the Z-port

parasitics appear directly across port-1 and port-2 respectively. Their circuit

arrangement is shown in Fig.

14.12

and has been shown to offer improved low

Search WWH ::

Custom Search