Hardware Reference

In-Depth Information

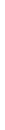

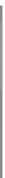

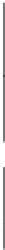

Fig. 2.1 Simplified form of

integrable CCII+ proposed

by Black et al. [

1

]

+V

+V

µA749C

Y

X

Q

1

+

−

Q

2

i

X

I

B

+ i

x

I

B

+ i

x

−V

i

X

Z

+V

I

B

I

B

I

B

R

B

Q

4

Q

3

Q

5

−V

therein removed for the sake of simplicity which have been included in the circuits

as presented in [

1

] for the purpose of reducing the errors in current followers due to

finite

β

). In the circuit of Fig.

2.1

, the uncommitted collector of Q

1

is connected to

the inverting input terminal of the op-amp thereby creating the port-X which will

therefore have V

x

¼

V

y

. From outside the chip four more transistors are added out

of which the transistors Q

3

-Q

4

-Q

5

constitute a current repeater such that the DC bias

current I

B

generated in the resistor R

B

through the diode connected Q

3

is mirrored in

Q

4

and Q

5

as shown. As a consequence, the collector current of Q

1

which is (I

B

+i

x

)

is duplicated in the external transistor Q

2

. Since the collectors of Q

2

and Q

5

are

connected together and the junction of these two constitutes the Z-terminal of the

CCII, it follows that current coming out of terminal-Z is exactly equal to the current

applied at terminal-X (taken as coming out of terminal-X for simplicity). Thus

i

z

¼

V

y

and i

y

is already zero, the circuit realizes a CCII+.

In the circuit schematic of Fig.

2.2

as many as seven external transistors have

been used. It may be seen that the desired DC bias current is created in the resistor

R

B

through two diode connected transistors Q

3

and Q

6

connected to DC power

supplies +V and

i

x

and since V

x

¼

V respectively which is mirrored into the collector of Q

5

through

the NPN current mirror Q

6

-Q

5

. Another replica of the DC bias current I

B

is created

in the collector of Q

4

through the PNP current mirror Q

3

-Q

4

. As in the earlier

circuit, the open collector of Q

1

is connected to the inverting input of the op-amp

and the collector of Q

5

thereby ensuring V

x

¼

V

y

(note that i

y

is already zero). It is

Search WWH ::

Custom Search