Hardware Reference

In-Depth Information

FG-DVCC

1

y

1

y

2

x

z

R

3

V

BP

FG-DVCC

2

y

1

y

2

z

V

LP

x

R

2

V

HP

y

1

y

2

V

in

z

V

BR

x

FG-DVCC

3

C

1

C

2

R

1

R

4

Fig. 12.8 VM multifunction filter configuration proposed by Khateb et al. (Adapted from [

11

]

©

2011 Elsevier Ltd.)

y

3

DVCC

1

DVCC

2

y

1

y

2

z+

y

2

z+

DVCC

3

y

2

y

1

V

out

x

z+

x

+

+

y

1

x

C

2

R

4

C

1

R

1

V

in2

R

2

+

V

in1

-

V

in3

-

R

3

-

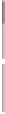

Fig. 12.9 VM universal filter proposed by Horng et al. [

12

]

Horng-Hsu-Tseng biquad

In Fig.

12.9

Horng et al. [

12

] have presented a VM MISO-type high input imped-

ance universal biquad filter circuit which employs three DVCCs and six passive

elements. The parasitic resistance of the X-terminal of the DVCC can be incorpo-

rated directly in the main resistances of each DVCC.

Assuming ideal DVCCs, the expression for output voltage in terms of input

voltages can be given by:

V

in

3

C

2

R

2

V

in

2

V

in

1

s

2

1

C

1

C

2

R

1

R

2

1

1

C

1

C

2

R

1

R

2

þ

s

R

4

R

3

C

2

R

2

R

3

V

out

¼

ð

12

:

34

Þ

R

4

1

C

1

C

2

R

1

R

2

s

2

þ

s

þ

Search WWH ::

Custom Search