Hardware Reference

In-Depth Information

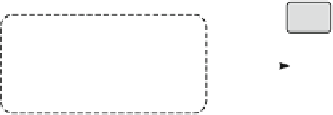

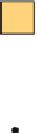

credit

updat

e

pipeline

register

outAvailable[0...N-1]

outPort

ready out[0...N-1]

CC

RC

SU

req

en

dst

outLock

Head flit

moves forward

SA

1

en

head

credit update

pipeline

register

head

granted

valid

valid

ready

ST

data

valid

data

data

Pipelined

Elastic Buffer

Output #j

Input #i

Fig. 5.17

The organization of a 3-stage pipelined router derived by the composition of RC and

SA pipeline stages that includes pipeline registers both in the control and the datapath of the router

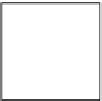

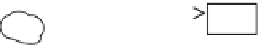

0

1

2

3

4

5

6

7

cc

s

SA-DQ

H

LT-BW

RC-EB

ST

LT-BW

cc

s

SA-DQ

B

LT-BW

EB

ST

LT-BW

cc

s

SA-DQ

T

LT-BW

EB

ST

LT-BW

cc

s

SA-DQ

H

LT-BW

RC-EB

ST

LT-BW

Fig. 5.18

The operation of a 3-stage pipelined router that exhibits no idle cycles by employing

pipeline registers at the end of RC and SA both in the control and data path of the router

and reaches its selected output, while the body flit that follows takes its place in

the data register of the SA stage after receiving a grant and consuming its credit.

The position previously held by the body flit is now occupied by the incoming tail

flit that has been dequeued from the input buffer and moved to the EB of the RC

stage. Cycle 4 evolves in a similar manner. Due to the two data pipeline registers,

the frontmost position of the input buffer is free for the head flit of the next packet

that arrived at the same input. This characteristic allows the head flit to complete

RC and move to the intermediate EB accordingly.

In this configuration, idle cycles are neither experienced by the flits of the same

packet nor by the flits across different packets, and all flits continue moving to their

selected output at full throughput. Any idle cycles experienced would be a result

of output contention due to the characteristics of the traffic pattern and the routing

algorithm, and not a result of the internal microarchitecture of the router.

Between the two extremes 3-stage pipelined solutions of using pipelining only

in the control path or both in the control and the data path, there are other two

intermediate configurations. The first one employs control pipeline at the RC stage

and combined pipelined at the SA stage, while the second does the opposite; it

employs combined pipelining at the RC stage and control-path-only pipeline in the

Search WWH ::

Custom Search