Hardware Reference

In-Depth Information

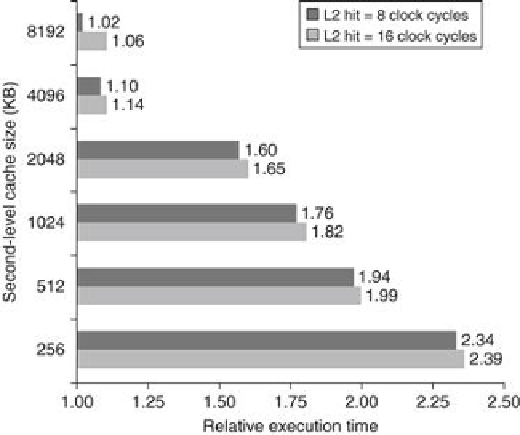

FIGURE B.15

Relative execution time by second-level cache size

. The two bars are for

different clock cycles for an L2 cache hit. The reference execution time of 1.00 is for an 8192

KB second-level cache with a 1-clock-cycle latency on a second-level hit. These data were

collected the same way as in

Figure B.14

,

using a simulator to imitate the Alpha 21264.

With these definitions in place, we can consider the parameters of second-level caches. The

foremost difference between the two levels is that the speed of the first-level cache affects the

clock rate of the processor, while the speed of the second-level cache only affects the miss pen-

alty of the first-level cache. Thus, we can consider many alternatives in the second-level cache

that would be ill chosen for the first-level cache. There are two major questions for the design

of the second-level cache: Will it lower the average memory access time portion of the CPI,

and how much does it cost?

The initial decision is the size of a second-level cache. Since everything in the first-level

cache is likely to be in the second-level cache, the second-level cache should be much bigger

than the irst. If second-level caches are just a litle bigger, the local miss rate will be high.

This observation inspires the design of huge second-level caches—the size of main memory in

older computers!

One question is whether set associativity makes more sense for second-level caches.

Example

Given the data below, what is the impact of second-level cache associativity on

its miss penalty?

■ Hit time

L2

for direct mapped = 10 clock cycles.

■ Two-way set associativity increases hit time by 0.1 clock cycle to 10.1 clock

cycles.

Search WWH ::

Custom Search