Hardware Reference

In-Depth Information

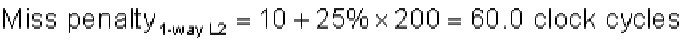

■ Local miss rate

L2

for direct mapped = 25%.

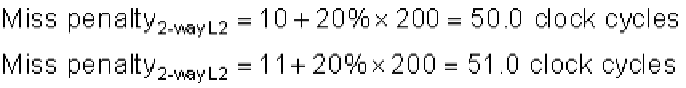

■ Local miss rate

L2

for two-way set associative = 20%.

■ Miss penalty

L2

= 200 clock cycles.

Answer

For a direct-mapped second-level cache, the first-level cache miss penalty is

Adding the cost of associativity increases the hit cost only 0.1 clock cycle,

making the new first-level cache miss penalty:

In reality, second-level caches are almost always synchronized with the irst-

level cache and processor. Accordingly, the second-level hit time must be an

integral number of clock cycles. If we are lucky, we shave the second-level hit

time to 10 cycles; if not, we round up to 11 cycles. Either choice is an improve-

ment over the direct-mapped second-level cache:

Now we can reduce the miss penalty by reducing the

miss rate

of the second-level caches.

Another consideration concerns whether data in the first-level cache are in the second-level

cache.

Multilevel inclusion

is the natural policy for memory hierarchies: L1 data are always

present in L2. Inclusion is desirable because consistency between I/O and caches (or among

caches in a multiprocessor) can be determined just by checking the second-level cache.

One drawback to inclusion is that measurements can suggest smaller blocks for the smaller

first-level cache and larger blocks for the larger second-level cache. For example, the Pentium

4 has 64-byte blocks in its L1 caches and 128-byte blocks in its L2 cache. Inclusion can still be

maintained with more work on a second-level miss. The second-level cache must invalidate all

first-level blocks that map onto the second-level block to be replaced, causing a slightly high-

er first-level miss rate. To avoid such problems, many cache designers keep the block size the

same in all levels of caches.

Search WWH ::

Custom Search