Hardware Reference

In-Depth Information

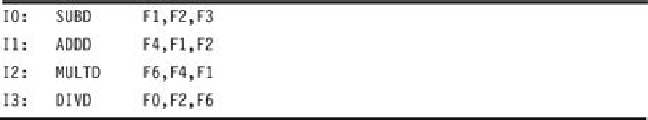

FIGURE 3.51

Sample code for superscalar register renaming

.

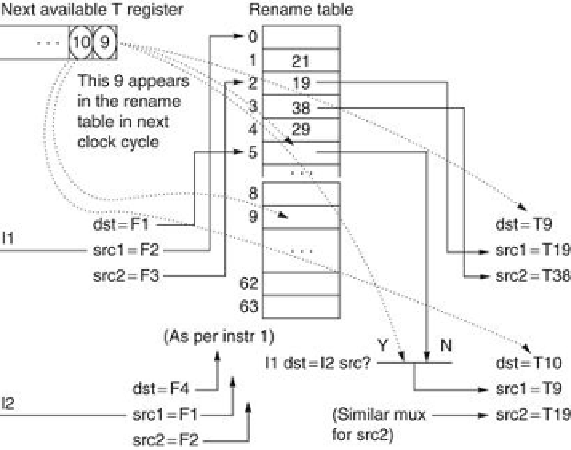

FIGURE 3.52

Rename table and on-the-fly register substitution logic for superscalar

machines

. (Note that

src

is source, and

dest

is destination.)

3.9 [5] <3.4> If you ever get confused about what a register renamer has to do, go back to the

assembly code you're executing, and ask yourself what has to happen for the right result to

be obtained. For example, consider a three-way superscalar machine renaming these three

instructions concurrently:

ADDI R1, R1, R1

ADDI R1, R1, R1

ADDI R1, R1, R1

If the value of

R1

starts out as 5, what should its value be when this sequence has executed?

3.10 [20] <3.4, 3.9> Very long instruction word (VLIW) designers have a few basic choices to

make regarding architectural rules for register use. Suppose a VLIW is designed with self-

draining execution pipelines: once an operation is initiated, its results will appear in the

destination register at most

L

cycles later (where

L

is the latency of the operation). There are

never enough registers, so there is a temptation to wring maximum use out of the registers

that exist. Consider

Figure 3.53

.

If loads have a 1 + 2 cycle latency, unroll this loop once,

Search WWH ::

Custom Search