Hardware Reference

In-Depth Information

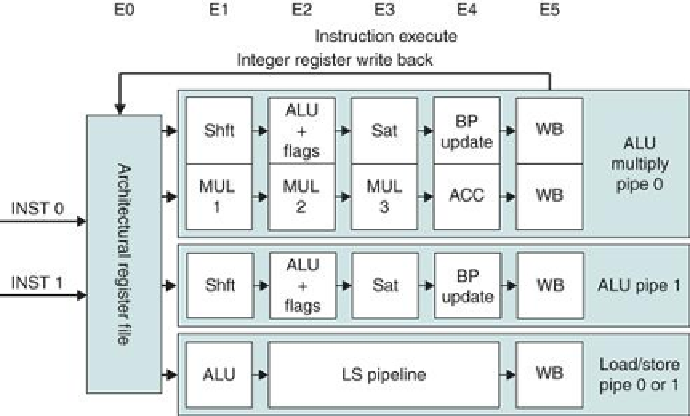

FIGURE 3.38

The five-stage instruction decode of the A8

. Multiply operations are always

performed in ALU pipeline 0.

Performance of the A8 Pipeline

The A8 has an ideal CPI of 0.5 due to its dual-issue structure. Pipeline stalls can arise from

three sources:

1. Functional hazards, which occur because two adjacent instructions selected for issue sim-

ultaneously use the same functional pipeline. Since the A8 is statically scheduled, it is the

compiler's task to try to avoid such conflicts. When they cannot be avoided, the A8 can is-

sue at most one instruction in that cycle.

2. Data hazards, which are detected early in the pipeline and may stall either both instruc-

tions (if the first cannot issue, the second is always stalled) or the second of a pair. The

compiler is responsible for preventing such stalls when possible.

3. Control hazards, which arise only when branches are mispredicted.

In addition to pipeline stalls, L1 and L2 misses both cause stalls.

Figure 3.39

shows an estimate of the factors that contribute to the actual CPI for the Min-

memory stalls are the major contributor to the CPI. This result is partially due to the effect that

Minnespec has a smaller cache footprint than full SPEC or other large programs.

Search WWH ::

Custom Search