Hardware Reference

In-Depth Information

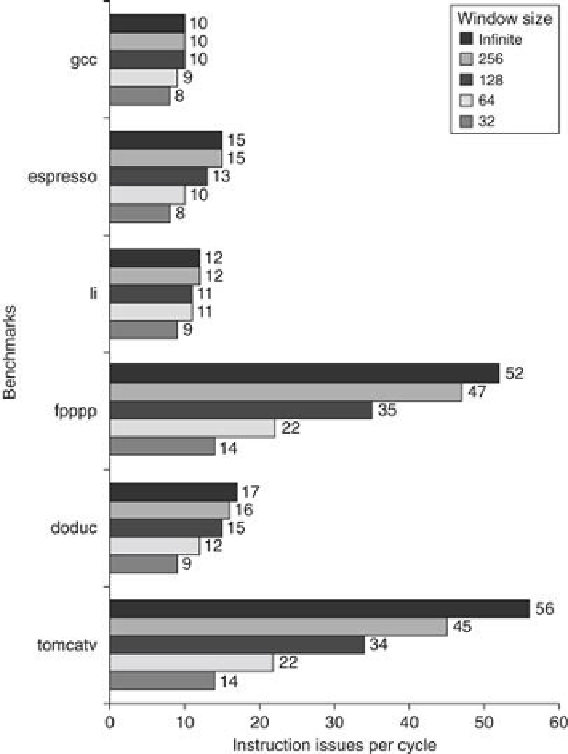

FIGURE 3.27

The amount of parallelism available versus the window size for a variety

of integer and floating-point programs with up to 64 arbitrary instruction issues per

clock

. Although there are fewer renaming registers than the window size, the fact that all op-

erations have one-cycle latency and the number of renaming registers equals the issue width

allows the processor to exploit parallelism within the entire window. In a real implementation,

the window size and the number of renaming registers must be balanced to prevent one of

these factors from overly constraining the issue rate.

In addition, remember that in interpreting these results cache misses and non-unit latencies

have not been taken into account, and both these effects will have significant impact!

The most startling observation from

Figure 3.27

is that, with the realistic processor con-

straints listed above, the effect of the window size for the integer programs is not as severe as

for FP programs. This result points to the key difference between these two types of programs.

The availability of loop-level parallelism in two of the FP programs means that the amount

of ILP that can be exploited is higher, but for integer programs other factors—such as branch

prediction, register renaming, and less parallelism, to start with—are all important limitations.

Search WWH ::

Custom Search