Image Processing Reference

In-Depth Information

Power supply integrity is thus a key for achieving higher performance of SoCs fabricated

using an advanced process technology. This is because degradation of the power integrity

causes a voltage drop across the power supply network, commonly referred to as the IR-drop,

which, in turn, causes unpredictable timing violations or even logic failures (Saleh et al.,

2000). To improve power integrity, highly accurate analysis of a power-supply network is

required. However, sophisticated SoCs, such as those for mobile phones, have many IPs and

many power domains to enable a partial-power-down mode in a single chip. Thus, many

spots of concentrated power consumption, called “hot spots”, appear at many places in the

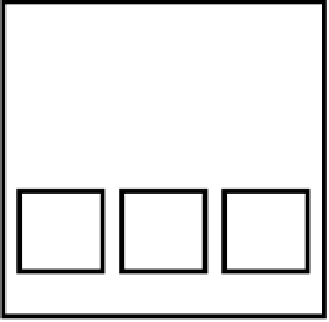

chip as shown in the Fig. 2. Analysis of the power-supply network is therefore becoming

more difficult. To address these issues, it is necessary to understand the influence of supply

noise in product-level LSIs, gain more knowledge of it, and improve evaluation accuracy in

the design of power supply networks via this knowledge. Above all, this understanding

is very important; therefore, in-situ measurement and analysis of supply-noise maps for

product-level LSIs has become more important, and can provide valuable knowledge for

establishing reliable design guidelines for power supplies.

CPU1

CPU2

CPU3

Hotspot:

Heavy current consumption part.

e.g. high speed operation, or

simultaneous operation of plural

circuits .

HW-IP1

HW-IP2

HW-IP3

Power gating switch to reduce

standby leakage current

consumption.

LSI

Fig. 2. Hotspots in the LSIs. The hotspots are defined as heavy current consumption parts in

the LSIs. The sophisticated LSI has many CPUs and hardware Intellectual Properties

(HW-IPs) in it, so the many hotspots become appearing.

In-depth analysis of the power supply network based on this in-situ power supply noise

measurement can be helpful in designing the power supply network, which is becoming

requisite for 65-nm process technology and beyond.

1.1 Related work

Several on-chip voltage measurement schemes have recently been reported (Okumoto et al.,

2004; Takamiya et al., 2004), and the features are illustrated in Fig. 3.

One such scheme involves the use of an on-chip sampling oscilloscope (Takamiya et al., 2004).

This function accurately measures high-speed signal waveforms such as the clock signal in

a chip. Achieving such high measurement accuracy requires a sample/hold circuit which

consist of an analog-to-digital converter (ADC) in the vicinity of the measurement point. This

method can effectively avoid the influence of the noise on the measurement. Therefore, a large

chip footprint is required for implementing measurement circuits such as a voltage noise filter,

a reference-voltage generator and a timing controller.