Hardware Reference

In-Depth Information

duce than DRAM chips. For example, a high-density DRAM chip might store up to 4Gb

(512MB) of RAM, whereas similar-sized SRAM chips can only store up to 72Mb (9MB).

ThehighcostandphysicalconstraintshavepreventedSRAMfrombeingusedasthemain

memory for PC systems.

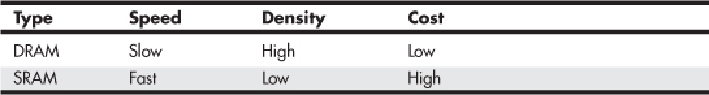

Table 6.1 Comparing DRAM and SRAM

EventhoughSRAMisimpracticalforPCuseasmainmemory,PCdesignershavefounda

waytouseSRAMtodramaticallyimprovePCperformance.Ratherthanspendthemoney

for all RAM to be SRAM memory, they design in a small amount of high-speed SRAM

memory, used as

cache memory

, which is much more cost effective. The SRAM cache

runs at speeds close to or even equal to the processor and is the memory from which the

processorusuallydirectlyreadsfromandwritesto.Duringreadoperations,thedatainthe

high-speed cache memory is resupplied from the lower-speed main memory or DRAM in

advance. To convert access time in nanoseconds to MHz, use the following formula:

1 / nanoseconds × 1000 = MHz

Likewise, to convert from MHz to nanoseconds, use the following inverse formula:

1 / MHz × 1000 = nanoseconds

Today we have memory that runs faster than 1GHz (1 nanosecond), but up until the late

1990s,DRAMwaslimitedtoabout60ns(16MHz)inspeed.Upuntilprocessorswererun-

ning at speeds of 16MHz, the available DRAM could fully keep pace with the processor

and motherboard, meaning that there was no need for cache. However, as soon as pro-

cessors crossed the 16MHz barrier, the available DRAM could no longer keep pace, and

SRAMcachebegantoenterPCsystemdesigns.Thisoccurredwaybackin1986and1987

with the debut of systems with the 386 processor running at speeds of 16MHz to 20MHz

orfaster.ThesewereamongthefirstPCsystemstoemploywhat'scalled

cache memory

,a

high-speed buffer made up of SRAM that directly feeds the processor. Because the cache

can run at the speed of the processor, it acts as a buffer between the processor and the

slower DRAM in the system. The cache controller anticipates the processor's memory

needs and preloads the high-speed cache memory with data. Then, as the processor calls

for a memory address, the data can be retrieved from the high-speed cache rather than the

much lower-speed main memory.

Cache effectiveness can be expressed by a hit ratio. This is the ratio of cache hits to total

memory accesses. A

hit

occurs when the data the processor needs has been preloaded in-