Image Processing Reference

In-Depth Information

Since the cross talk level depends on the degree of oblique incident ray, high-level condi-

tions are required for imaging optical elements such as taking lenses.

As already noted, BSIs have an advantage for making effective use of incident light.

However, because the sensing material is silicon, whose absorption coefficient in the vis-

ible light region is low, and the color filter is thick, a light shield film is necessary to sup-

press cross talk. Since it restricts the aperture ratio, it can be said that the potential of BSIs

is not currently maximized. Excellent performances are not always achieved with BSIs, but

high-level technique is also needed to achieve mastery.

As will be shown in the next section, the advantages of optical performance that appealed

at first, such as sensitivity and incident angle dependence, are not maintained compared

to advanced FSIs. On the contrary, BSIs have a disadvantage from the viewpoint of cost-

benefit performance. This is an example of a technique that has an advantage for mono-

chrome cameras but does not necessarily have the same advantage also for SCCC systems.

The differences in sensors for monochrome systems and single-chip color systems should

be recognized.

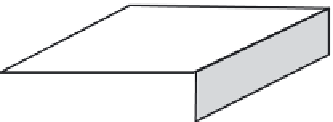

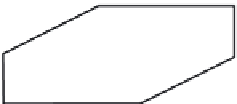

As a recent innovation in BSIs, stacked BSIs

58

have attracted much attention. In conven-

tional BSIs, the supporting substrate plays the role of sustainer, without any other function,

although it is made of silicon wafer, as shown in Figure 5.70a. In stacked BSIs, it is com-

posed of a top part (die) and a bottom part (die), as shown in Figure 5.70b. While the pixel

array, row drivers, load transistors, and comparators are formed in the top part, the control

circuits, row decoder, reference voltage, counter, image processing, and output interface

are arranged in the bottom part. They are stacked with the top part up and connected by

a through-silicon via (TSV), which is a type of vertical via-type contact. The top part is a

CMOS image sensor (CIS) process made of one polysilicon and four metal layers (1P4M),

including a color filter and OCL. The bottom part is implemented by a 65 nm 1P7M logic

process. In conventional BSIs, an expensive CIS process has to be used for the entire die,

but in stacked BSIs, the most appropriate process can be applied to fabricate each die. This

is expected to compensate somewhat for the above-mentioned disadvantage of conven-

tional BSIs because of the cost-effective inclusiveness of chip size shrinkage made possible

by the CIS process. It is expected that the introduction of various functions will extend this

technology to three-dimensionally integrated image sensors. Pixel-level processed image

sensors including ADCs might become reality sooner rather than later.

The most advanced BSI and the most advanced FSI are comparable in optical performance

such as sensitivity and incident angle dependence, as will be discussed in Section 5.3.3.3.3.

Pixels

Pixels

Circuits

Circuits

Supporting

substrate (Si)

Logic process

substrate (Si)

(a)

(b)

FIGURE 5.70

Structure of stacked CMOS image sensor: (a) conventional BSI; (b) stacked BSI. (Reprinted with permission from

Sukegawa, S., Umebayashi, T., Nakajima, T., Kawanobe, H., Koseki, K., Hirota, I., Haruta, T. et al.,

Proceedings of

the IEEE International Solid-State Circuits Conference, Digest of Technical Papers

, 27.4, pp. 484-486, 2013.)