Image Processing Reference

In-Depth Information

exposure. A typical ESV is controlled by a switching arrangement that provides the

measuring condition in which charge is induced on a probe electrode corresponding to

the sensed voltage level on the photoconductor. The induced charge is proportional

to the sum of the internal capacitance of the probe and its associated circuitry relative

to the probe-to-measured surface capacitance. A DC measurement circuit is combined

with the ESV circuit for providing an output that can be read by a conventional test

meter or used as input to the feedback control computer. The surface voltage is a

measure of the density of the charge on the photoconductor, which is related to the

quality of the printed output. There is typically a routine within the operating system of

the printer to periodically create test areas (called patches) [9,10] at predetermined

locations on the photoconductor by deliberately causing the exposure system to charge

or discharge as necessary for measurement with the ESV. To avoid negative impact on

productivity, color patches are created in small unobtrusive areas, such as the inter

document zone (IDZ), between the latent images as illustrated in Figure 9.3.

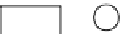

A block diagram representation of the level 1 control system is shown in Figure

9.4. The exposed patch area voltage level, Vl,

l

, and an unexposed patch area voltage

level, V

h

, are shown in the diagram with the actuators, the grid voltage, U

g

(also

denoted by V

g

for later use) , and the exposure intensity, Ul

l

(also denoted by X for

later use). The desired goals for the feedback system is to maintain the charge

(and hence voltages Vl)

h

and V

l

) on a moving photoconductor surface to desired set

points

(

V

h

and

V

l

respectively).

Control patches

Photoconductor

Latent

image

area

Latent

image

area

Latent

image

area

FIGURE 9.3

IDZ patches (shows typical patches used for measuring exposed and unex-

posed areas of the CMYK separations using four ESVs).

U

go

-

+

u

1

+

k

11

+

Integrator

Electrostatic

charging and

exposure

system

E

h

u

g

U

g

+

V

h

V

h

k

21

Sensor

values

k

12

k

22

u

l

E

1

+

Integrator

+

U

l

V

l

+

u

2

+

V

l

-

Controller

Target

values

U

lo

FIGURE 9.4

Block diagram representation of the level 1 electrostatic control loop.

Search WWH ::

Custom Search