Information Technology Reference

In-Depth Information

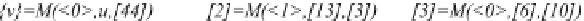

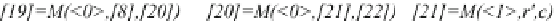

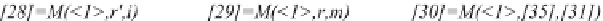

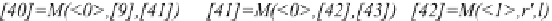

ð

21

Þ

Comparing Eqs. (

20

) and (

21

), it can be seen that the proposed method uses 6

levels and 37 majority gates while the method in [

15

] uses 9 levels and 46 gates. The

number of levels is reduced by 33.3 % and the number of gates used is reduced by

19.6 %. The circuit diagrams for the results obtained by both methods are shown in

Figs.

18

and

19

.

More benchmark comparisons are provided in Table

2

. It can be seen that on

average, there is 8.13 % reduction in terms of majority gates and 7.94 % reduction in

terms of logic levels by the proposed method as compared to the best existing

method [

15

].

Search WWH ::

Custom Search