Information Technology Reference

In-Depth Information

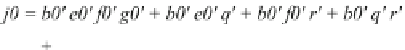

ð

19

Þ

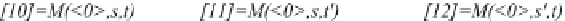

The SIS tool is used to simplify the circuit and decompose it into a four-feasible

network. Then the process introduced in Sect.

4.4

is applied to each node of the

network to obtain its majority expression. After removing the redundancies, the final

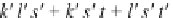

result is shown in Eq. (

20

). Logic ''1'' and ''0'' are represented as ''\1['' a n d ''\0[''

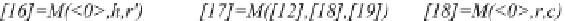

in the majority expression network because some circuits use ''1'' or ''0'' to name

their variables. For comparison purpose, the output from the synthesis method in [15]

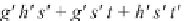

is shown in Eq. (

21

)

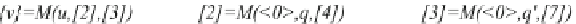

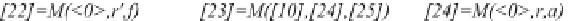

ð

20

Þ

Search WWH ::

Custom Search