Information Technology Reference

In-Depth Information

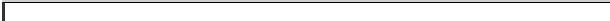

Table 1.

Comparison of Flexicache with Architecture Based Error Correction Schemes

for Scaling Vcc (Bold is better)

Segmented

2D ECC

Disabling/

Flexicache

ECC

Bit-Fix

Persistent Failures

yes

yes

yes

yes

Non-Persistent Failures

yes

yes

no

yes

Minimum

V

dd

375 mV

-

400 mV

320 mV

(see Section 5)

Latency in the

1cycle

1cycle

0cycle

1cycle

Low-Power Mode

Other Latency

no

read-modify-write

no

no

of this scheme is strongly dependent upon the location of defective bits. So that,

it is not convenient to use in low-power mode when failures are random. Also,

it requires a read-modify-write operation for all Stores and for every cache miss

which increases the delay and power consumed by all write operations. Miller

et al. [23] proposed Parichute which utilizes Turbocodes for reducing

V

dd

of the

second and higher level caches. Although this scheme provides a very high error

correction rate supporting a voltage reduction significantly, its error correction

latency can be couple of cycles (i.e. more than 5 cycles [23]) in the near-threshold

voltage level. Thus, Parichute is not convenient to be used in time-critical L1

caches. Several disabling schemes have been proposed for tolerating only persis-

tent failures [30,3,5]. Wilkerson et al. [30] disables the faulty words in order to

combine two consecutive cache lines to form a single cache line where only non-

failing words are used. Although the area overhead of word-disable in high-power

mode is only 8%, in the low power mode the available cache size shrinks to the

half when the error rate is lower than 0.01%. Abella, et al. [3] disables sub-blocks

instead of words in order to utilize more capacity in the low-power mode. Both

disabling schemes need to access a fault map in parallel. ZerehCache [5] employs

fine granularity re-mapping of faulty bits and relies on solving a graph coloring

problem to find the best re-mapping of defects to spare lines. Bit-fix [30] stores

the location of defective bits and their correct values to the quarter of cache

ways. Circuit-based hardening approaches have also been proposed such as us-

ing 8T SRAM cells [24] which are more stable against parameter variations than

6T cells. 8T cells are useful for noisy places and specially designed for low

V

dd

modes while it presents high area overhead in the nominal voltage.

In this study, we propose Flexicache, a circuit-driven solution that duplicates

or triplicates all the available lines in the cache with no increase in the access

latency. We presented the preliminary sketch of the idea for the circuit design in a

previous event without precluding further submissions [26]. In this study, besides

elaborating the circuit design, we present the details of the address decoder and

the architectural extensions of Flexicache.

3 Architecture of Flexicache

Flexicache allows three modes of error protection according to the resilience level

of the applied

V

dd

: Single Version Mode (SVM), Double Version Mode (DVM)