Java Reference

In-Depth Information

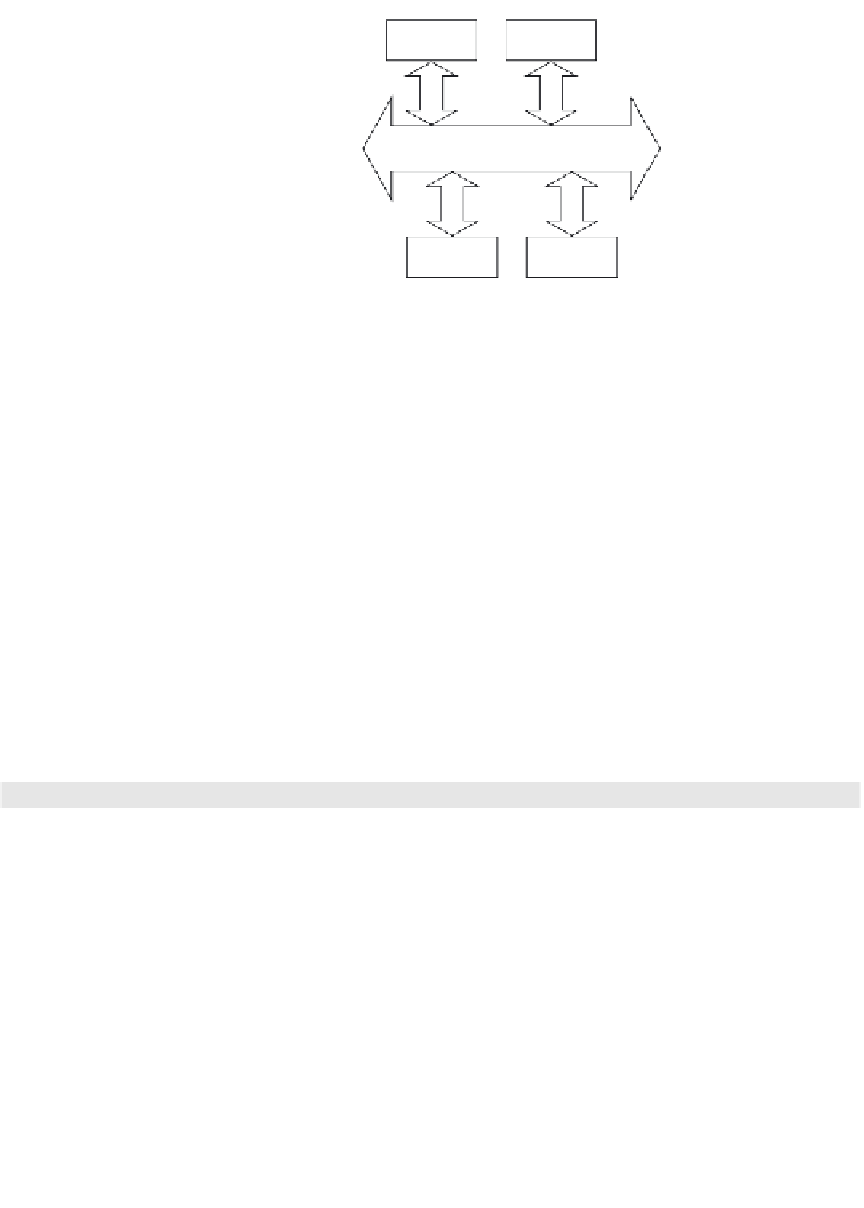

CPU

RAM

Bus

I/O

Storage

Figure 5.1

The Von Neumann architecture

The goal is to develop a simulation tool that allows monitoring of the

behaviour of individual components during the execution of test programs

written in an assembly-like programming language. Test programs are stored

in the form of textual files and loaded by the simulation tool at start-up.

The simulation must emphasize the behavioural properties over temporal

ones. Thus, time and performance will not be a concern.

5.1.1

The instruction set

We consider an architecture based on the simple instruction set defined in

Table 5.1. Instructions are made up of two parts: the code and the argument.

The code describes the type of operation to be performed (e.g. moving data

from the memory to a register). The argument, when present, is the index of

a memory location; it is used to perform the operation.

Table 5.1

Instruction set

Code

Argument

Description

Halts the CPU

HALT

address

Jumps to the instruction at the given address

JUMP

address

Jumps to the instruction at the given address if register A contains zero

JUMPZ

address

Load register A with the content of the cell at address

LOADA

address

Load register B with the content of the cell at address

LOADB

address

Store the content of register A in the cell at address

STOREA

address

Store the content of register B in the cell at address

STOREB

Store the content of register A in the memory whose address is contained

in register B

MOVEAB

Add the content of register A to the content of register B and put the result

into register A

ADD

address

Read information from the I

O and store it in the cell at address

INPUT

address

Read information from the cell at address and send it to I

O

OUTPUT

address

Open a file whose name is found in the cell at address

FOPEN

address

Read information from the currently open file into the cell at address

FREAD

Close the previously opened file

FCLOSE