Information Technology Reference

In-Depth Information

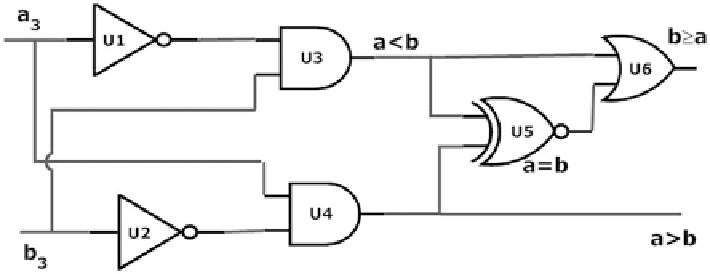

Fig. 6.10

Typical stage of a magnitude comparator for bits a

3

, b

3

and d

e are signal labels. They denote a physical label-to-label connec-

tion even though a path is not shown (portrayed this way for clarity).

The outputs a

e or d

>

1 MUX, similar to the MUX above.

This MUX is connected to send the highest priority values to a third comparison

block U5. Here the logic is such that the highest priority forces to true one of the

outputs of the AND gates. This identifies that image with the higher priority.

b and d

e control a 2

>

>

Comparator Design

Units 1, 2, 5 are standard binary magnitude comparators [

5

]. Figure

6.10

shows a

typical stage. Such comparators are based on XOR gates to compare binary

numbers beginning with the most significant bits. If these are equal, the next most

significant bits are processed. Note that U5 is an exclusive NOR, which is an XOR

with a NOT gate to invert the output. Sometimes U5 is termed an equality gate since

its output is true if the inputs are equal.

Timing Estimations

If there is only one associative return, there is no need for a priority determination.

In this case the image is gated into short-term memory immediately (provisions for

this are not shown). Going through associative memory likely requires only a few

tens of milliseconds.

Gamma brain waves display synchronized oscillations in the range of 30-90 Hz

and are a possible correlate of consciousness. A rate of images moving through

conscious short-term memory might be taken to be 40 Hz. This means a refreshed

image about every 25 ms, although no doubt this can vary considerably. A cycle

time of a few tens of milliseconds, say 25 ms, is comparable with the basic rate in

the above system.

Search WWH ::

Custom Search