Execute

The execution circuitry is centered around the Arithmetic Logic Unit (ALU) – see Fig. 2.19.The ALU processes data from up to two sources. One of these is the 8-bit Working register. The other can be multiplexed either from a file in the Data store or an 8-bit literal, which is part of the instruction code. For example addwf 20h,w and addlw 5 respectively add the contents of W to that of File 20h or the constant 5 to W. The outcome can be switched back into W (eg. addwf 20h,w) or into the register file (eg. addwf 20h,f) as controlled by the single Destination bit in the instruction code.

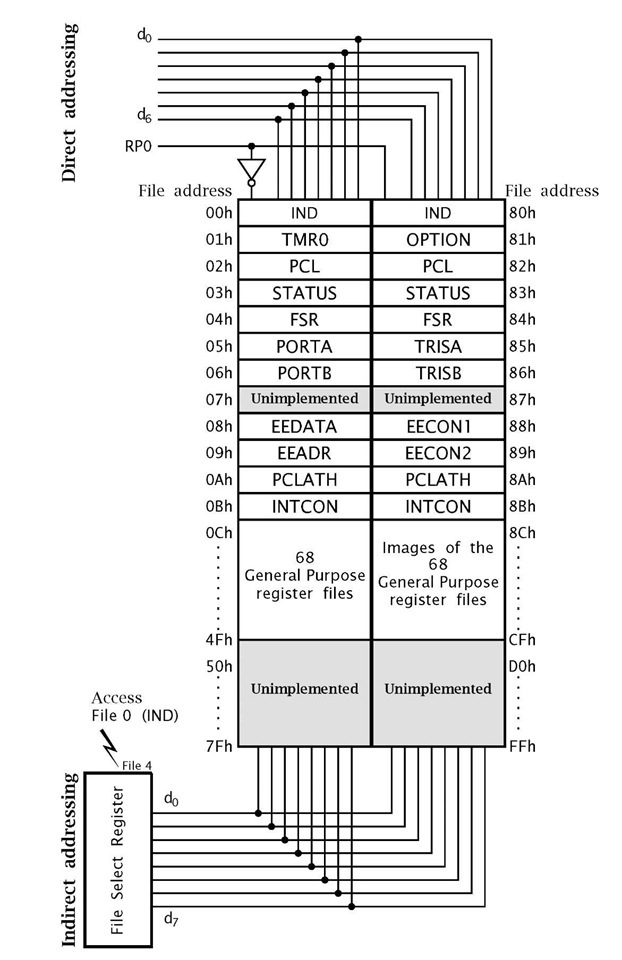

Where an operand is a file, the execution unit can generate the Data store address in one of two ways – see Fig. 4.6.

• Directly via a 7-bit address field in the instruction.Seven bits can only directly address up to 128 files. This can be increased to 256 files if the state of the RP0 bit in the Status register (see Fig. 4.5) is also multiplexed in as part of the Data store address.

• Indirectly using the File Select Register in conjunction with Indirect addressing, as described in Fig. 3.6. In this situation the 8-bit address in the FSR is used to address the Data store whenever the virtual location File 0 is addressed. Here potentially all 256 files in both banks can be addressed irrespective of the state of RP0.

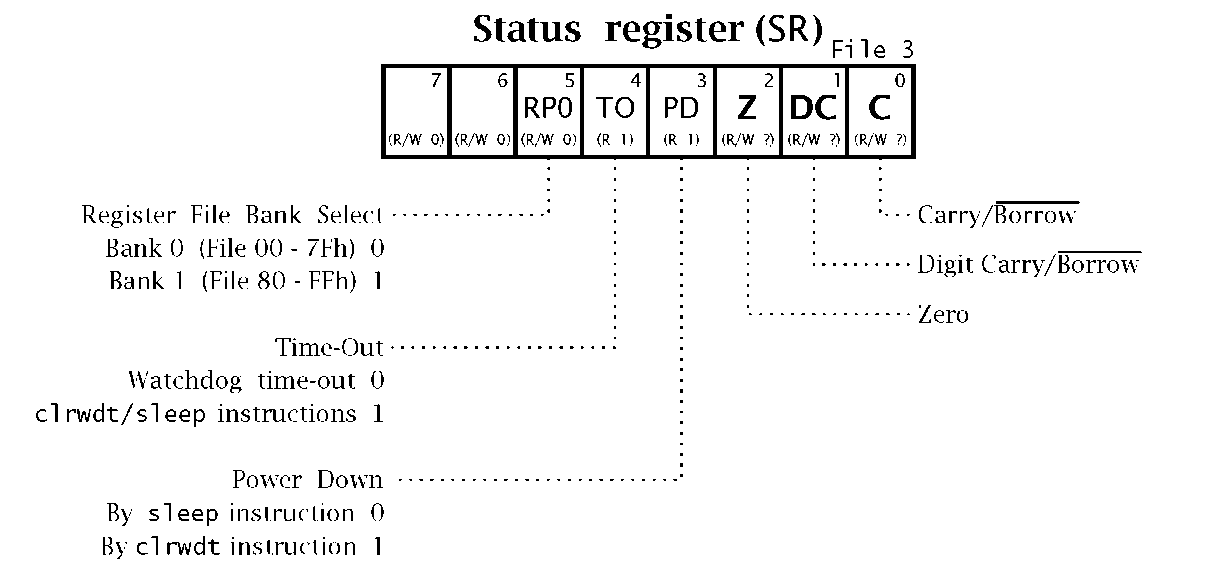

The three flag bits in the Status register STATUS are associated with the ALU, giving status information concerning the outcome from an instruction.

Carry flag

Bit 0 of the Status register is the C flag. This primarily holds the Carry out from the last addition operation. Subtraction operations activate this bit as the complement of the Borrow out. For example, 24 – 12 = 12E1 and 12 – 24 = 88B0. C also functions as an input/output bit for the Rotate instructions, as shown in Fig. 3.7.

The label R/W ? in Fig. 4.5 indicates that this bit can be read from or written to and has an indeterminate value on a power-up reset – its value does not alter on any other type of reset.

Digit Carry flag

Bit 1 of the Status register is the DC flag. This operates in the same manner as the standard C flag but holds the Carry out from the lower nybble to the upper nybble; that is from bit 3 to bit 4. In the same manner DC holds the complement of the Borrow out from bit 3 to bit 4. Knowledge of the Carry activity between the lower and upper halves of the byte is useful where binary coded decimal data is being manipulated. Here each nybble holds a 4-bit representation of the decimal digits 0.9 and the half carry then indicates carries between decimal decades.

Zero flag

Bit 2 of the Status register is the Z flag. This is set whenever the outcome of the instruction is zero, otherwise it is cleared.

Fig. 4.5 The PIC16F84 Status register

Unlike most MCUs, there are no instructions to specifically clear or set a flag, such as sec for SEt Carry.17 However, as the Status register is accessible as a file in the Data store, then any instruction that can alter the contents of a file can potentially change the state of a flag. There is a potential problem in that many of these instructions affect one or more flags (see Table 3.1) as part of their execution logic and this overrides any change that would result from the outcome of the instruction’s execution. For example, clrf 3 actually sets the Z flag to 1 . The Bit Clear File and Bit Set File instructions are recommended where an individual bit in the Status register needs to be altered, as these instructions do not inherently affect these flags. For instance, bsf 3,0 (Set Bit 0 in File 3) is equivalent to sec and bcf 3,2 (Clear Bit 2 in File 3) is equivalent to clz.

STATUS also holds the RP0 bank switching bit. The TO and PD readonly bits shown in Fig. 4.5 give information on what type of reset last occurred (Power-Up when power was applied to the device, Watchdog when the Watchdog timer timed out or External by bringing the MCLR pin low) or if awakened from the sleep instruction. As these are designated as read-only, they cannot be altered as part of the software, only monitored. These status bits will be discussed in Part 3 of the topic.

In the normal Harvard manner, the execution unit is separated from the fetch unit, with distinct data bus, address bus and stores. It is of course controlled via the Instruction decoder which is fed from the bottom of the pipeline in the fetch unit. The fetch Program Counter is in the Data store’s address space so the execution unit can effect the fetch sequence by altering the Program Counter, as shown in Program 6.4.

The execute unit is also sequenced by the same four clock phases as the fetch unit operating in parallel.

Q1: Decode instruction.

Q2: Read from Data store.

Q3: Process data in ALU.

Q4: Write into Data store.

Program store

The majority of PIC devices use EPROM for program memory. As EPROM can only be erased using UV radiation (see Fig. 2.11) once the software has been programmed into the Program store it can be considered effectively permanently in situ. Such devices are known as One-Time Programmable (OTP). Where it is likely that program code will need to be subsequently altered, the MCU may be housed in a ceramic package with a quartz window, allowing for erasure in around 20 minutes.

An alternative approach is to implement the Program store using EEP-ROM technology.This allows the ‘fixed’ data to be erased electrically without the expense of a UV transparent package and the time delay inherent with this technology. Using this approach, code can even be reprogrammed in the field, to subsequently upgrade software, without the device having to be removed from the circuit board. Thus, say, a modem’s algorithm or a PC’s BIOS can be upgraded over a computer network by the user. Microchip’s strategy is to substantially increase the number of EEPROM devices but at the time of writing (2000) most devices are EPROM based.

The 16F84 holds its program code in an internal flash EEPROM memory18 holding 1024 (210) instructions, each of 14-bits width. This memory is accessed from the fetch unit via the 14-bit Program data bus into the pipelined Instruction register 1, and is addressed via the Program address bus by the lower ten bits of the Program Counter PC[9.. .0]. The address range is 000…3FFh. As the Program Counter is 13 bits wide, other members of the 14-bit core family can potentially interact with a 213 = 8 kbyte-instruction Program store; for example, the PIC16F876/7.

All members of the mid-range PIC family use address 000h as the Reset vector (the place the PIC goes to when it is reset, for the startup of the program) and 004h for the Interrupt vector – the place the PIC goes to whenever it gets an interrupt request.

Data store

The Data store comprises 81 8-bit locations known as file registers or just files for short. The contents of any location in the Data store may be moved into or out of the Working register. The PIC16F84′s file registers are located in the Data store’s memory map as shown in Fig. 4.6. The registers can be categorised as Special-Purpose Registers (SPRs) used by the core CPU and peripheral modules for status information and controlling the desired operation of the device. The remaining implemented General-Purpose Registers (GPR) can be used by the programmer for temporary storage of program variables.

There are two ways an instruction can target a datum in the Data store. Each file register has an address, which is listed in Fig. 4.6. For example PORTA is located at File 05.

Directly

Any instruction which can process a datum in the Data store can directly specify the effective address using seven binary bits which are part of the binary program code. By itself this can address a base range of 00-7Fh. However, we see from Fig. 4.6 that this address is augmented by the RP0 bit19 in the Status register to give an effective 8-bit address. If RP0 is 0 (as it is after reset) the range is 00-7Fh, that is Bank0. If RP0 is made 1 then the range is 80-FFh; that is Bank1. For example, to set the contents of File register TRISB (File 86h) to all 1 s and then to read the contents of the File register PORTB into the Working register, we need the following program:

Fig. 4.6 Data store memory map.

Indirectly

If the Indirect address mode is used, as was described in Fig. 3.6, then the 8-bit address in the File Select Register (FSR) is used as the effective. As we have an 8-bit address in this situation any location in the two banks are accessible with not bank switching required. The same example as described above is then implemented as:

Although there is no Bank switching required, this code segment is actually longer than the previous solution! However, Indirect addressing is useful when one location in Bank 1 requires frequent access.

The bottom 12 locations of both banks are reserved for SPRs. Although the exact location can vary across members of the mid-range family, common registers; for example, PCL and PORTA tend to have the same location.

Of these, we have already met most of those involved with the core function: INDF

The INDirect File at File 0 is not physically implemented as a register. Instructions accessing this virtual location actually put the contents of the FSR onto the Data store address bus, as described in Fig. 3.6.

The Program Counter Low byte is addressed as File 2. Its relationship with the total 13-bit PC is described on Fig. 4.3.

The Status register can be accessed in File 3. As can be seen from Fig. 4.5, this file holds the three code condition bits plus several status bits and the Data store page bit RP0.

The File Select Register at File 4 holds the indirect address used when the instruction refers to the virtual INDF address.

File 0Ah holds the LATch High byte for the Program Counter, as described in Fig. 4.3.

The INTerrupt CONtrol register at File 0Bh holds the mask and status bits controlling the response of the MCU to interrupts. Its operation is described in topic 7.

All these core SPRs are images in both memory banks.

The remaining nine SPRs relate to the configuration and control of the various peripheral interface devices. More details will be given on individual peripheral SPRs in Part 3 of the topic in the appropriate topics.

The 68 GPRs are located from File 0Ch through File4Fh and are mirrored in Bank 1.20 Thus the instruction clrf 4Fh and clrf 0Cfh are identical and target the same physical location irrespective of the state of the Register Page bit RP0 setting. The remaining file locations are not implemented and read as 00h, as does location File 07h/File 87h – which is reserved for PORTC and TRISC in devices with 28+ pins.

Peripheral functions

Each member of the PIC family has its unique set of integrated peripheral devices. However, all PICs have parallel input/output and timer facilities. As well as these standard facilities, the PIC16F84 has a peripheral 64-byte EEPROM which can be used as a small data store not dependent on continuous power to retain its contents; i.e. non-volatile.

Each of these peripheral facilities are described in detail in Part 3 of the topic, but for completeness are briefly cataloged here together with their associated SPRs. These registers are used to configure the function of their target peripheral interface, to control and monitor their status.

Parallel input/output

The ability to externally alter or monitor several digital lines at the same time is a virtually universal facility on microprocessor-based systems.

Apart from the 8-pin PIC12XXX series, all PICs have a minimum of 12 such external input/output lines. Some have much more, such as the 40-pin PIC16C74 which has 33 I/O lines.

The PIC16F84 has 13 I/O lines, divided up into two ports. Port A has five I/O lines mapped into the Data store address space at File 5. The remaining eight lines are allocated to PortB at File 6. These ports can be thought of as a ‘window’ into the Data store in that data written to File 5 or File 6 appear to the outside world on the corresponding pins; pins RA4…RA0 and RB7…RB0 respectively. However, the electrical and logic behavior of these ports is more complex than that of a purely internal register file. This will be discussed in topic 11 but as an example a port bit must be configurable as either an output (so that the CPU can control the state of the associated pin) or an input (so that the CPU can read the state of this pin). To do this, each Port register has an associated Data Direction register, which Microchip call TRISA and TRISB, which map to File 85h and File 86h respectively (the term TRIS stands for TRIState.These registers lie in the less convenient Bank 1 as they are usually set up at the beginning of the program and never subsequently altered.

As an example, consider that we wish to make Port B bits 6.0 an input and bit 7 an output. Then the setting up code would be:

As an example, subsequently pin RB7 can be pulsed high and then low as follows:

with the assumption that the CPU is still in Bank0. The registers associated with parallel I/O are:

Only the lower five bits are implemented in this register file, feeding through to pins RA4.RA0. Pin RA4 is shared with the Timer peripheral. The upper three bits read as zero.

This is used to bitwise configure Port A bits as input or output. Setting TRISA[n] to 1 sets bit PORTA[n] as an input and to 0 as an output. Any type of reset sets the TRIS bits to 1 and the associated port bits to input.

A bi-directional 8-bit port connected to pins RB7…RB0. Bit RB0 doubles as a hardware interrupt input.

This is used to bitwise configure Port B bits as input or output. Details are the same as TRISA.

![tmp18290_thumb[2] tmp18290_thumb[2]](http://what-when-how.com/wp-content/uploads/2011/06/tmp18290_thumb2_thumb.png)

![tmp18291_thumb[2] tmp18291_thumb[2]](http://what-when-how.com/wp-content/uploads/2011/06/tmp18291_thumb2_thumb.png)

![tmp18292_thumb[2] tmp18292_thumb[2]](http://what-when-how.com/wp-content/uploads/2011/06/tmp18292_thumb2_thumb.png)

![tmp18293_thumb[2] tmp18293_thumb[2]](http://what-when-how.com/wp-content/uploads/2011/06/tmp18293_thumb2_thumb.png)