T flip flops can of course be cascaded, as shown in Fig. 2.22(a). Here four ^ triggered flip flops are chained, with the output of binary n clocking binary n + 1. Thus if the input Count frequency was 8 KHz, then Qa would be a 4 kHz square waveform and similarily QB would measure in at 2 kHz, QC at 1 kHz, QD at 500 Hz.

Fig. 2.22 A modulo-16 ripple counter.

The waveform QA of Fig. 2.22(b) was derived in the same manner as in Fig. 2.21. Qb is toggled on each ^ of QA and likewise for the subsequent outputs. Marking a high as logic 1 and a low as logic 0 gives the 24 (16) positive-logic binary patterns as time advances, with the count rolling over back to state 0 on a continual basis. Each pattern remains in the register until the next event clocks the chain; an event being defined in our example as a ^ at Count. Examining the sequence shows it to be a natural 8-4-2-1 binary up count, incrementing from 0000b to 1111b. In fact the circuit is a modulo-16 binary counter. A modulo-n count is the sequence taking only the first n numbers into account.8

In theory there is no limit to the number of stages that can be cascaded. Thus using eight T flip flops would give a modulo-256 (28) counter. In practice there is a small propagation delay through each stage and this limits the ultimate frequency. For example the 74LS74 dual D flip flop of Fig. 2.16 has a maximum propagation from an event at its Clock input to output of 25 ns. The maximum toggling frequency for a single stage, such as in Fig. 2.21, is given as 25 MHz. An 8-stage counter thus has a maximum ripple-through time of 200 ns. If such a ripple counter were clocked at the resulting 5 MHz (201>ns) then no sooner than one particular code pattern has stabilized then the next one would begin to appear. This is only really a problem if the various states of the counter are to be decoded and used to control other logic. The decoding logic, such as shown in Fig. 2.23, may inadvertently respond to these short transient states and cause havoc. In such cases more sophisticated synchronous counter configurations are more applicable where the flip flops are clocked simultaneously and steered by the appropriate logic configuration to count in the desired sequence.

The circuit illustrated here implements an up count. If the complement Q lines are used as the outputs, but with the clocking arrangements remaining the same, then the count sequence will decrement, that is a down count. Likewise using _/ triggered flip flops, such as the 74LS74 dual flip flop (see Fig. 2.23), are used as the storage element, then the count will be down. It is easily possible to use some simple logic to combine the two functions to produce a programmable up/down counter. It is also feasible to provide logic to load the flip flop array in parallel with any number and then count up or down from that point. Such an arrangement can be thought of as a parallel-in counting register.

Fig. 2.23 Generating timing waveforms.

As well as the more obvious use of a counter register to totalize the number of events, such as cans of peas coming along a conveyor belt, there are other uses. One of these is to time a sequence of operations. In Fig. 2.23 a modulo-4 counter is used to address one section of a 74LS139 2 to 4-line decoder, see Fig. 2.5(a). This detects each of the four states of the counter, and the outcome is four time-separated outputs that can be used to sequence, say, the operation of a computer’s control section logic. As a practical point, the complement Q flip flop outputs have been used to address the decoder to compensate for the _/ triggered action that would normally give a down count. Larger counters with the appropriate decoding circuitry can be used to generate fairly sophisticated sequences of control operations.

The term register is commonly applied to a read/write memory that can store a single binary word, typically 4-64 bits. Larger memories can be constructed by grouping n such registers and selecting one of n. Such a structure is sometimes known as a register file. For example, the 74LS670 is a 4 x 4 register file with a separate 4-bit data input and data output and separate 2-bit address. This means that any register can be read at any time, independently of any concurrent writing process.

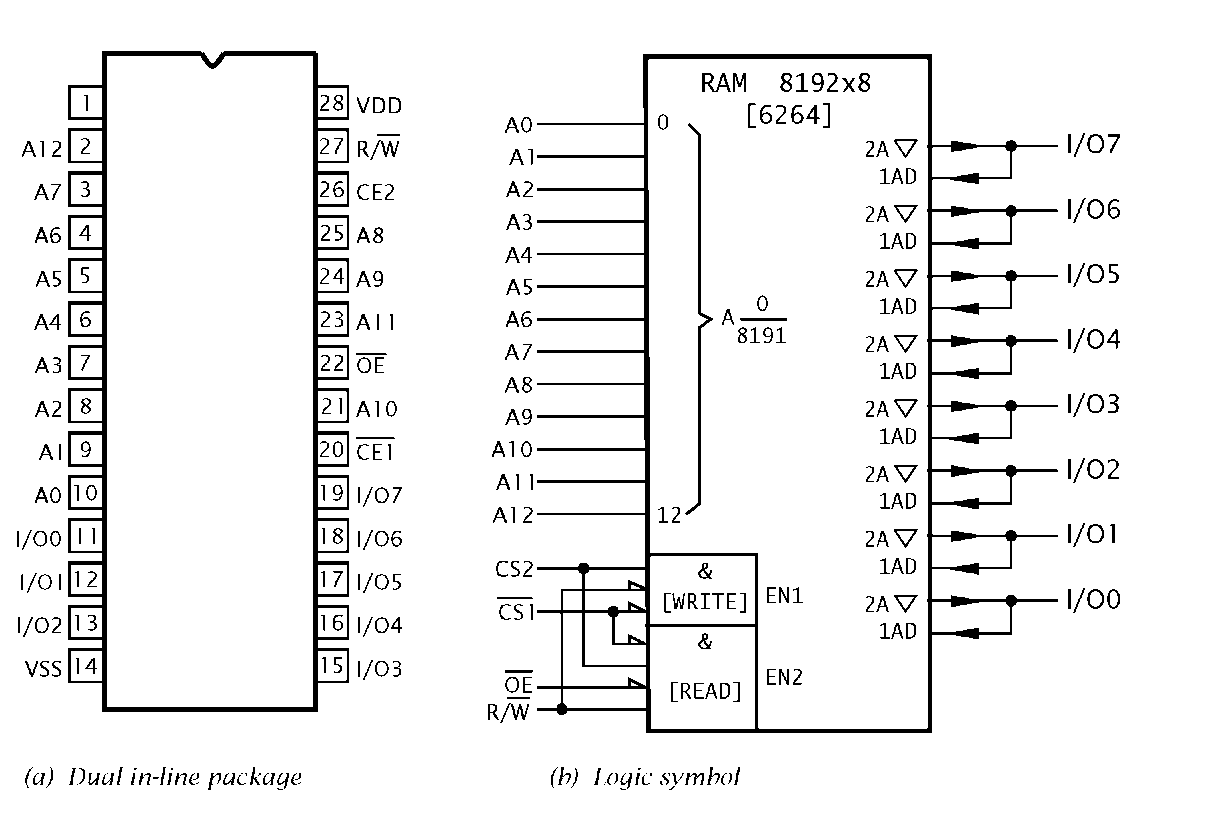

Fig. 2.24 The 6264 8196 x 8 RAM.

Larger read/write memories are normally known as read-write Random-Access Memories, or RAMs for short. The term random-access indicates that any memory word may be selected with the same access time, irrespective of its position in the memory matrix.9 This contrasts with a magnetic tape memory, where the reel must be wound to the sector in question – and if this is at the end of the tape!

For our example, Fig. 2.24 shows the 6264 RAM. This has a matrix of 65,536 (216) bistables organized as an array of 8192 (213) words of 8 bits. Word n is accessed by placing the binary pattern of n on the 13-bit Address pins A12…A0. _

When in the Read mode (Read/Write = 1), word n will appear at the eight data outputs (I/07…I/00) as determined by the state n of the address bits. The A symbol at the input/outputs (as was the case in Fig. 2.11) indicates this addressibility. In order to enable the 3-state output buffers, the Output Enable input must be Low.

The addressed word is written into if R/W is Low. The data to be written into word n is applied by the outside controller to the eight I/O pins. This bi-directional traffic is a feature of computer buses.

In both cases, the RAM chip as a whole is enabled when CS1 is Low and CS2 is High. Depending on the version of the 6264, this access from enabling takes around 100 – 150 ns. There is no upper limit to how long the data can be held, provided power is maintained. For this reason, the 6264 is described as static (SRAM). Rather than using a transistor pair bistable to implement each bit of storage, data can be stored as charge on the gate-source capacitance of a single field-effect transistor. Such charge leaks away in a few milliseconds, so needs refreshed on a regular basis. Dynamic RAMs (DRAMs) are cheaper to fabricate than SRAM equivalents and obtainable in larger capacities. They are usually found where very large memories are to be implemented, such as found in a personal computer. In such situations, the expense of refresh circuitry is more than amortized by the reduction in cost of the memory devices.

Both types of Read/Write memories are volatile, that is they do not retain their contents if power is removed. Some SRAMs can support existing data at a very low holding current and lower than normal power supply voltage. Thus a backup battery can be used in such circumstances to keep the contents intact for many months.