Combined RF Pre-Amplifier and Mixer Design

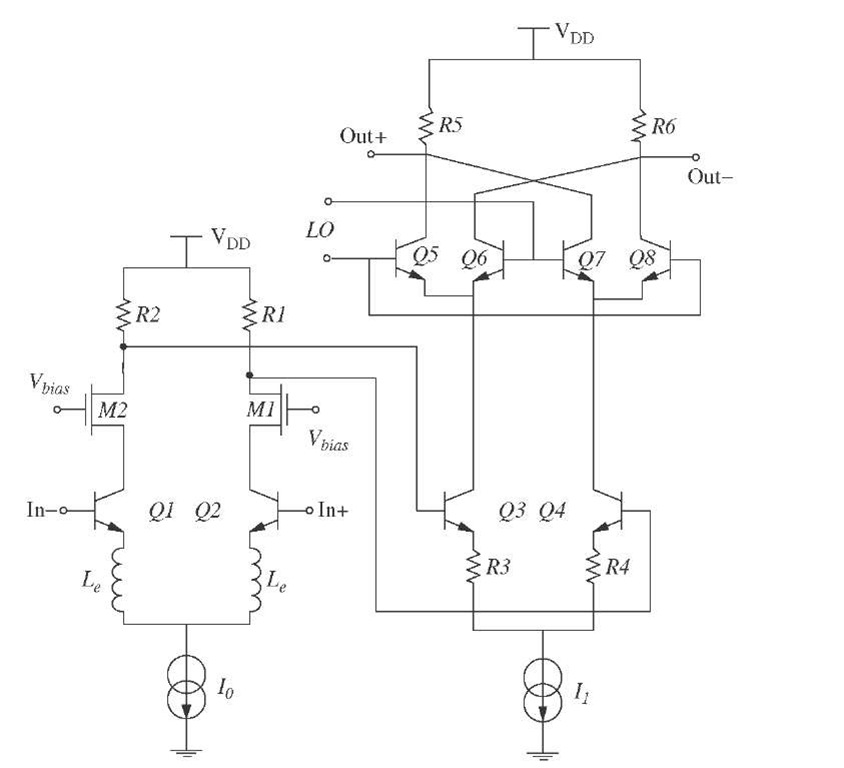

As previously explained, a relatively high-gain receiver configuration has been chosen. For this reason, the RF mixer has been implemented using a differential input amplifier plus a Gilbert cell. Figure 3-15 shows the final simplified circuit diagram.

Taking previous design considerations into account, the input impedance of the Gilbert cell has been set to optimise the power consumption, gain, NF, and linearity of the entire RF mixer. If the input impedance is increased by degenerating the Gilbert cell, the gain of the cell will be lower and the NF will be higher. Those effects can be minimised by increasing the gain of the preceding RF amplifier. As the load of the amplifier will be higher due to higher input impedance of the Gilbert cell, no extra power will be needed to increase the gain of the RF amplifier. This results in low power consumption and the improvement of linearity of the entire RF mixer as well as the linearity of the Gilbert cell.

On the other hand, to avoid degrading the performance of the RF mixer, the LO power level must guarantee the appropriate switching performance of the mixer core. The local oscillator power level should be between -10dBm and -3dBm in the designed Gilbert cell, which input impedance differs from the standard 50Q. Due to this high power value, the isolation between the LO input and the IF output must be high enough to avoid feedthrough and interference problems. To suppress the LO signal at the IF output, a differential Gilbert cell and external filtering have been used.

Figure 3-15 Simplified schematic of the down-conversion stage (differential amplifier + Gilbert cell)

Layout Considerations and Simulation Results

Figure 3-16 shows a microphotograph of the designed frequency down-conversion block. The pre-amplifier and its emitter degenerating inductances can be identified in the middle of the microphotograph, just above the down-conversion mixer. The RF, IF, VDD, and GND pads surround both blocks (pre-amplifier and mixer).

Common centroid techniques have been used with all the elements of the pre-amplifier and the mixer to avoid linearity degradation and to improve LO/RF and LO/IF isolation. That plays a big part in avoiding re-radiation of the LO signal through the LNA and the antenna as well as LO signal saturation or interference with the IF signal. RF pads have a hexagonal shape and are manufactured with only the top thick metal layer to minimise parasitic capacitance. The size of the pre-amplifier and mixer chip (including decoupling capacitors and pads) is 1.25x 1.1mm2.

Figure 3-16 RF pre-amplifier and mixer microphotograph

Double pads are used for VDD and GND to allow double bondwires in order to reduce their parasitic inductance. This minimises AC ground and supply loops resulting from bondwire and package parasitic inductances, reducing the risk of pre-amplifier oscillation.

As in the case of the LNA, different parasitic effects have been taken into account in order to perform simulations of realistic situations. Effects of PAD parasitic capacitances, bondwire inductances, bondwire coupling between different pins, and package parasitics are included in the simulation setup to facilitate the obtaining of realistic results.

The specification values reported in the previous topic and post-layout results of the down-conversion block are shown in Table 3-5.

The design presents a lower NF and current consumption than specified, but at the cost of lower gain. The extra needed gain, caused by the low gain of the mixer, will be supplied by the IF amplifier. This will ensure that the initial overall receiver gain specification will be met. The linearity, OIP3, is just 1dB (0.5dBm) lower than specified (1.5dBm). It will only slightly influence the interference blocking capacity of the receiver, resulting in satisfactory front-end performance.

TABLE 3-5 Post-layout results

|

Parameter |

Specifications |

Post-layout |

Unit |

|

S11 |

-20.2 |

dB |

|

|

OIP3 |

1.5 |

0.5 |

dBm |

|

Gain |

23 |

18.1 |

dB |

|

NF |

6.2 |

5.6 |

dB |

|

Current |

5.9 |

mA |

IF Limiting Amplifiers and Filters

The design of two IF LC filters is covered in the IF stage. The first one is located next to the RF down-conversion mixer. The second one is located between the first and second IF limiting amplifiers (see Figure 3-1). The IF filters provide the following functions:

■ They define and shape the noise bandwidth to be amplitude-quantized by the 1bit ADC.

■ They provide the required selectivity to protect the IF limiting input from spurious signals that pass through the RF SAW filters, typically 20MHz wide.

■ They attenuate undesired second mixer output products, such as the LO leakage or mixer second harmonics, to levels that will not block the IF limiter amplifier.

■ They can reject spurious common mode and/or differential signals generated by high-level on-chip sources, such as reference clock harmonics.

Two IF limiting amplifiers have been considered in the system analysis. Both are preceded by an LC filter, which is located next to the mixer and the first amplifier respectively. They provide the gain required to digitalise the incoming GPS signal. The noise figure is not a key parameter because of its low contribution to the total noise, as stated by the Friis equation [Razavi97], since it is not included in the early stages of the front-end, but after the LNA, the RF amplifier, and the down-conversion mixer.

Figure 3-17 shows the basic cell of the IF amplifier. It is a differential common source architecture due to its high voltage gain as well as its high input and output impedance. The load for the first amplifier (IF1) comes from the second IF amplifier (IF2) and the second IF filter, where the load for the second IF amplifier (IF2) comes from the 1bit ADC.

Figure 3-17 IF basic cell amplifier schematic

As mentioned before, implementing a 1bit ADC is considered to be the last stage in the chain of the front-end. Therefore, above a minimum level, amplitude of the ADC input signal is insignificant because only negative-to-positive transitions, or vice versa, are detected. For this reason, clamping diodes can be used without any information loss, as shown in Figure 3-18. In addition, the amplitude of the amplifier output signal will be limited. Clamping of the output signal will allow the input switches of the ADC latches to work properly, minimising any current leakage. It is important to keep in mind that the clamping diodes also load the amplifier. Therefore, small diodes are recommended to avoid degrading of the frequency response.

To implement the amplifier chain, various basic stages are connected in cascade to obtain the required gain. Thus, IF1 is built with three basic stages in cascade and an output common drain stage to match the output impedance to the LC filter, as shown in Figure 3-19. The load resistance of the third basic stage has been decreased to 6kQ in order to reach the required bias voltage for the common collector output stage. Figure 3-20 shows the IF2 amplifier, which consists of two basic stages.

Figure 3-17 shows the basic cell used for the IF amplifier. The load resistance (RL), the bias current of the differential amplifier (Idq), and the width of the transistors (W) are considered to be design variables. The length of the transistors (L) is fixed at 1.3|im. Due to size mismatch problems, a larger value than the minimum 0.35|im is set to minimise the input offset of the differential pair.

Figure 3-18 IF limiting amplifier with clamping diodes (diodes or MOS transistors)

Figure 3-19 IF1 amplifier chain

Figure 3-20 IF2 amplifier chain

By examining the IF amplifier small-signal equivalent circuit presented in Figure 3-21, the gain and the dominant pole of the system can be obtained from Eq. 3-33 and Eq. 3-34, respectively.

where Eq. 3-35 and 3-36 are as follows:

Figure 3-21 Simplified IF amplifier small-signal equivalent circuit

Therefore, the system transfer function can be roughly expressed as shown in Eq. 3-37:

where w1 is the frequency of the pole. Based on these equations and verified by simulations, optimal design variables values have been set to the values shown in Table 3-6.

The LC values of the external IF filters are shown in Table 3-7. The required extra capacitance to set the central frequency of the IF filter to 20.4MHz is added on chip.

![tmpE465_thumb2[2] tmpE465_thumb2[2]](http://what-when-how.com/wp-content/uploads/2012/02/tmpE465_thumb22_thumb.jpg)

![tmpE466_thumb2[2] tmpE466_thumb2[2]](http://what-when-how.com/wp-content/uploads/2012/02/tmpE466_thumb22_thumb.jpg)

![tmpE468_thumb2[2] tmpE468_thumb2[2]](http://what-when-how.com/wp-content/uploads/2012/02/tmpE468_thumb22_thumb.jpg)