Information Technology Reference

In-Depth Information

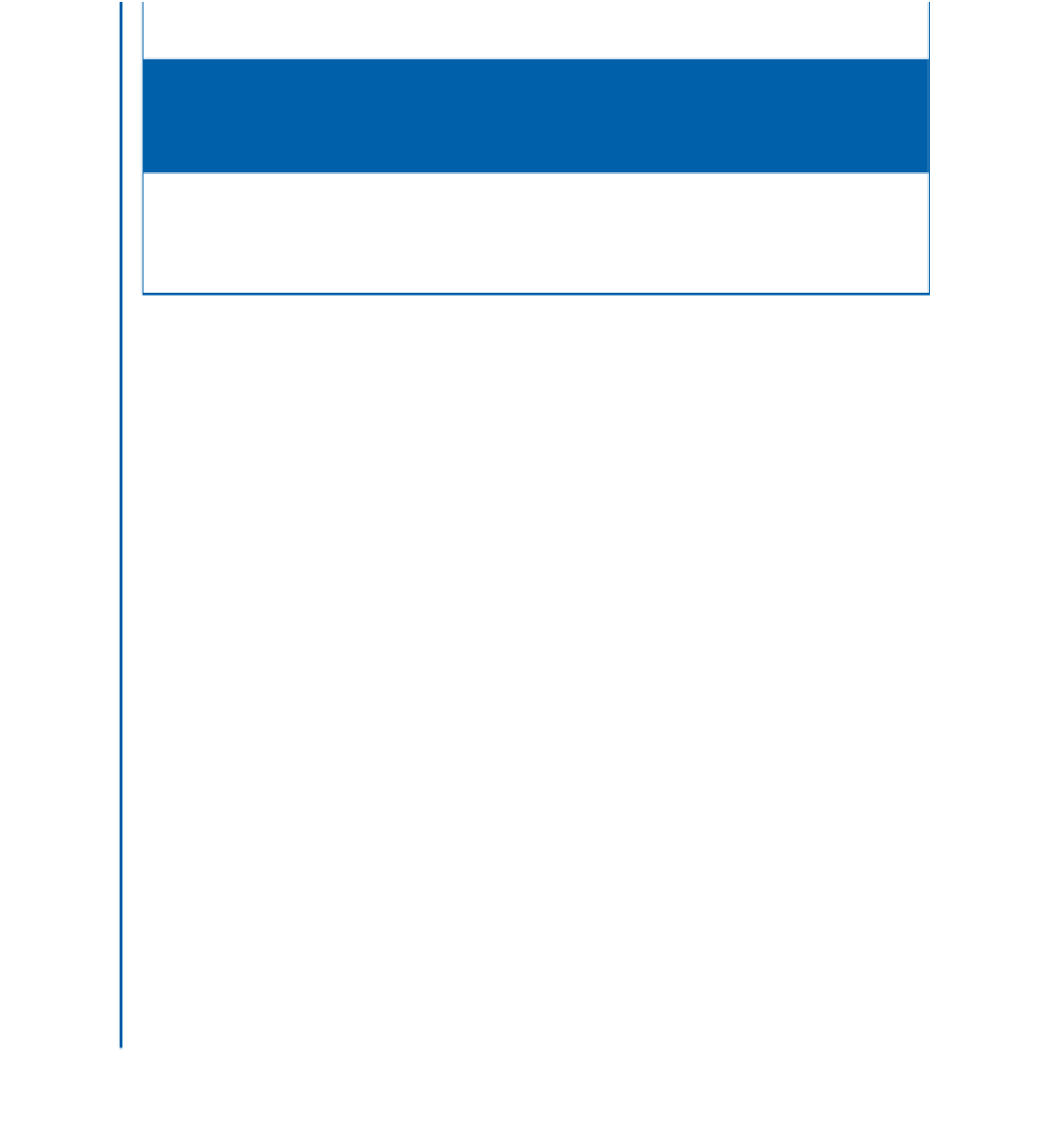

TABLE 4.6:

Rules for Switching to Low-power Modes. Adapted from [

19

].

Trigger

Threshold Values

Enable Condition 4-issue

(

I

IPC

<

3

.

0) AND (FP

IPC

<

1

.

4) with hysteresis

of two windows

Disable Condition 4-issue

(

I

IPC

>

3

.

2) OR (FP

IPC

>

1

.

6)

Enable Condition 6-issue

(

I

IPC

<

4

.

5) AND (FP

IPC

<

1

.

4)

Disable Condition 6-issue

(

I

IPC

>

5) OR (FP

IPC

>

1

.

6)

integer and floating IPC) to a set of empirically derived thresholds. There is also hysteresis

for the decision to go to the lowest power mode (the 4-issue mode) requiring the enabling

conditions to hold for two consecutive sampling windows. The actual rules used are listed

in Table 4.6, where I

IPC

and FP

IPC

are the issue IPC for the integer and the floating point

instructions, respectively.

These rules for adjusting the width of the machine result in minimal performance loss (on

the order of 1-2%) for both single applications and multiprogramming workloads while realizing

at times satisfactory per-component power savings (on the order of 10-15%). However, in the

big picture, the power savings for the whole processor are not as dramatic. Bahar and Manne

point out that a single technique alone cannot solve the power consumption problem. Rather,

by taking a holistic approach and applying many techniques in concert, power consumption

can be brought down significantly.

4.8 IDLE-CAPACITY SWITCHING ACTIVITY: CACHES

Similarly to instruction queues, caches can also be

sized

to save power. Although it is always

better to have more cache, in many cases using much less can save considerable power while

giving up very little in performance.

Considerable work is devoted to the general problem of reducing dynamic power in

caches. Here, we are only concerned with techniques that

resize

the cache to fit program needs.

Techniques that optimize cache access but do not really change the amount of cache available

to the programs are discussed extensively in Section 4.9. We concentrate on four proposals

that have inspired further work: a cache resizing proposal that trades memory between two

cache levels [

7

,

21

], the

selective cache ways

proposal [

8

] which resizes a cache by changing

its associativity, the

accounting cache

proposal [

68

] which is a combination of the two previous

proposals, and finally a CAM-tag cache resizing technique [

244

]. Table 4.7 summarizes the

Search WWH ::

Custom Search