Information Technology Reference

In-Depth Information

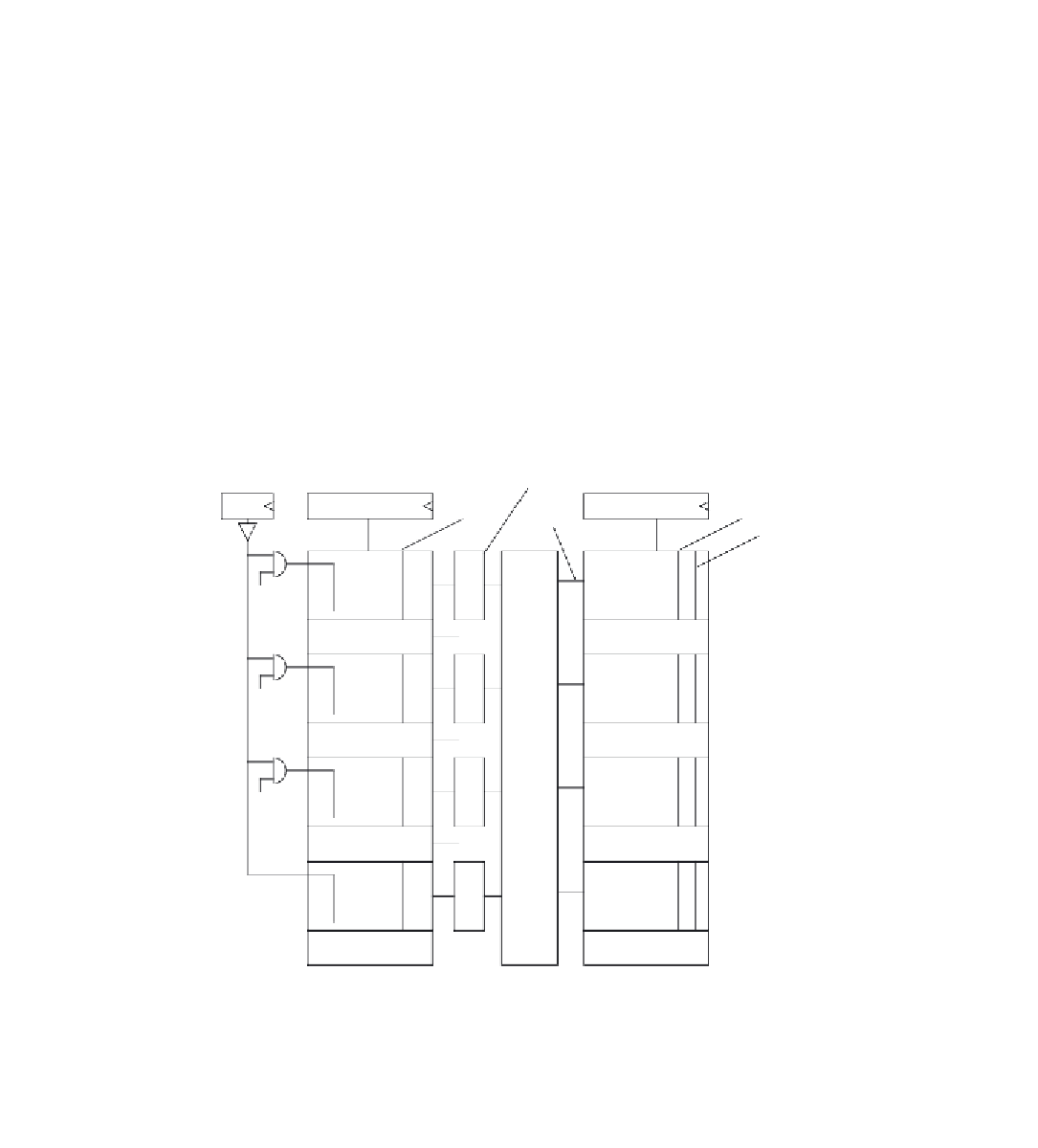

The paper discusses a detailed circuit-level implementation of a resizable (adaptive) issue queue

(IQ)—conceptually similar to Albonesi's complexity-adaptive design. More interestingly, the

paper proposes a high-level mechanism for adaptation [

42

]. The design of the IQ is a mixed

CAM/SRAM design where each entry has both CAM and SRAM fields. The SRAM fields

hold instruction information (such as opcode, destination register, status, etc.) and the CAM

fields constitute the wakeup logic for the particular entry, holding the input operand tags.

Results coming from functional units match the operand tags in the CAM fields and select the

SRAM part of the entry for further action. When an instruction matches both its operands it

becomes “ready” to issue and awaits to be picked by the scheduler.

The IQ is divided in large “chunks” with transmission gates placed at regular intervals

on its CAM and SRAM bit-lines. The tag match in the CAM fields is enabled by dedicated

taglines

. Partitioning of the IQ in chunks is controlled by enabling or disabling the transmission

gates in the bit-lines and the corresponding taglines. Figure 4.13 shows the design.

Wakeup logic

Ready flags

Bit-line

Bit-line

Dummy Bit-line

Wordline

CAM

SRAM

en3

transmission gate

transmission gate

en3

en3

CAM

SRAM

en2

transmission gate

transmission gate

en2

en2

CAM

SRAM

en1

transmission gate

transmission gate

en1

en1

CAM

SRAM

Precharge / SenseAmp

Precharge / SenseAmp

Instruction Read

FIGURE 4.13:

The design of an adaptive Instruction Queue. Enable signals (en

X

) enable the CAM

and SRAM parts. Adapted from [

42

].

Search WWH ::

Custom Search