Information Technology Reference

In-Depth Information

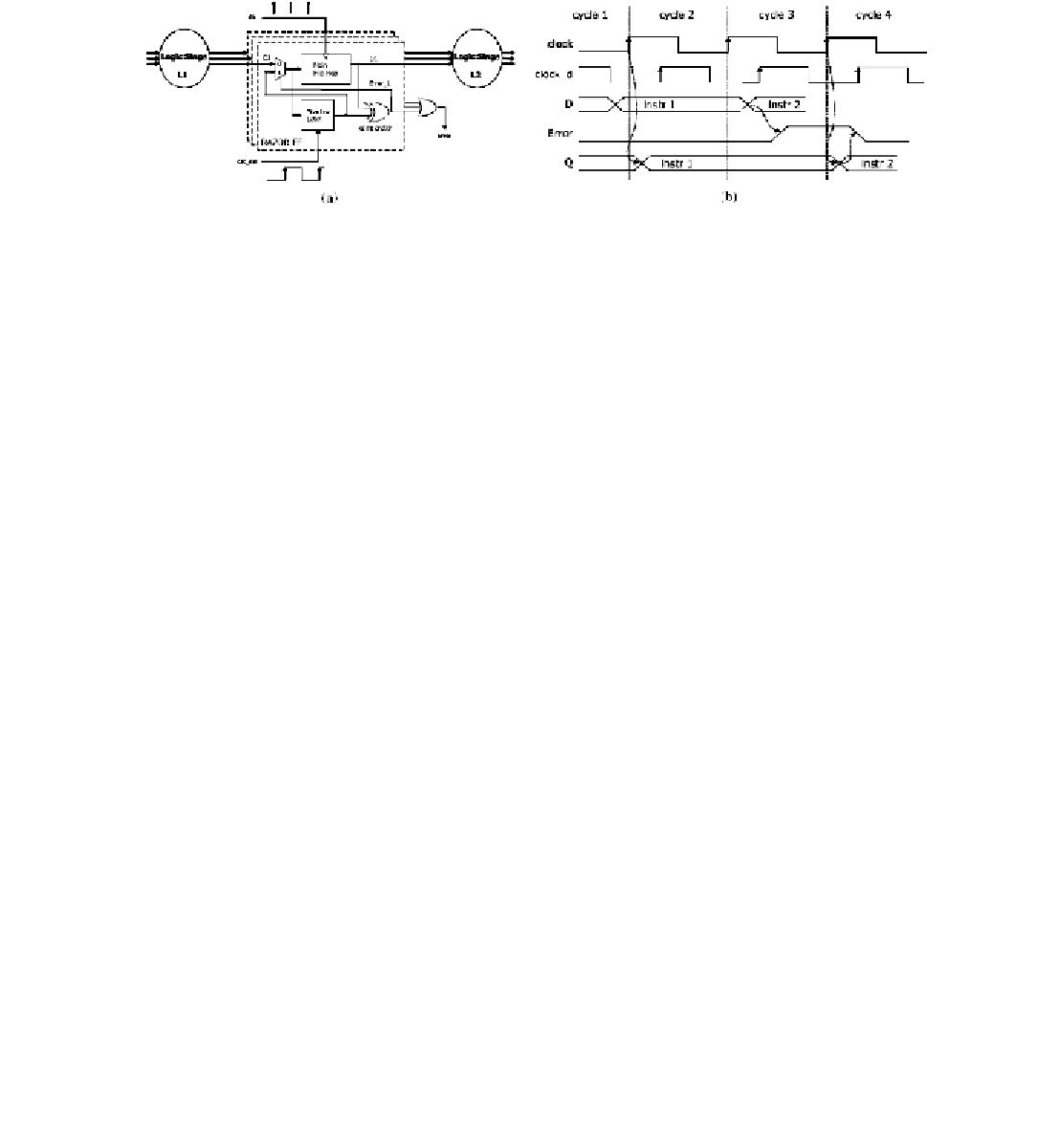

FIGURE 3.8:

Razor flip-flop (on the left). Example operation (on the right). In cycle 2, incorrect results

of the logic stage L1 are latched in the main latch. This is detected by the Razor flip-flop and the error

is signaled in cycle 3. The error is corrected, the main latch receives the correct value from the shadow

latch and operation is resumed in cycle 4. Reproduced from [

73

]. Copyright 2003 IEEE.

occur because worst-case conditions appear very infrequently. On the other hand, the more

voltage is reduced below the critical level, the more likely faults become.

The idea behind Razor is to lower the voltage until

timing faults start to occur

.These

timing faults are detected by the hardware itself using special, “safe” flip-flops that detect

timing violations. Something analogous can be done by tuning the supply voltage during

processor operation to meet a predetermined delay through an embedded inverter delay chain.

This global approach still requires margins in the voltage levels, since it does not account for

local variations. In contrast, Razor adapts dynamically to

local

conditions.

The

Razor flip-flop

(Figure 3.8) double-samples pipeline stage values: once with the fast

clock and a second time with a time-delayed clock. This is done by using two latches. The main

latch latches the data on the fast clock. A

shadow latch

, controlled by the time-delayed clock,

latches the data for the second time. To guarantee that shadow latches always latch correct data,

subcritical voltage is constrained at design time to levels that allow the shadow latch set-up

times to exceed the delay of the logic—even in worst-case conditions.

The values latched by the main latch and the shadow latch are then compared with a

metastability-tolerant comparator. If the values sampled with the fast clock are the same with

those sampled with the delayed clock then no error has occurred. This is the common case. If,

however, a timing error occurred then the values do not match. In this case, an error signal is

raised by the faulting flip-flop.

The error signal restores the incorrect value of the main latch using the value of the

shadow latch. All other Razor flip-flops in the same pipeline stage are also restored (regardless

of whether they have generated a timing error). To recover the whole pipeline after a Razor

error, two techniques can be used. The first uses clock gating to stall the whole pipeline for a

single cycle so that the correct values can be restored in the flip-flops. Operation then resumes

Search WWH ::

Custom Search