Information Technology Reference

In-Depth Information

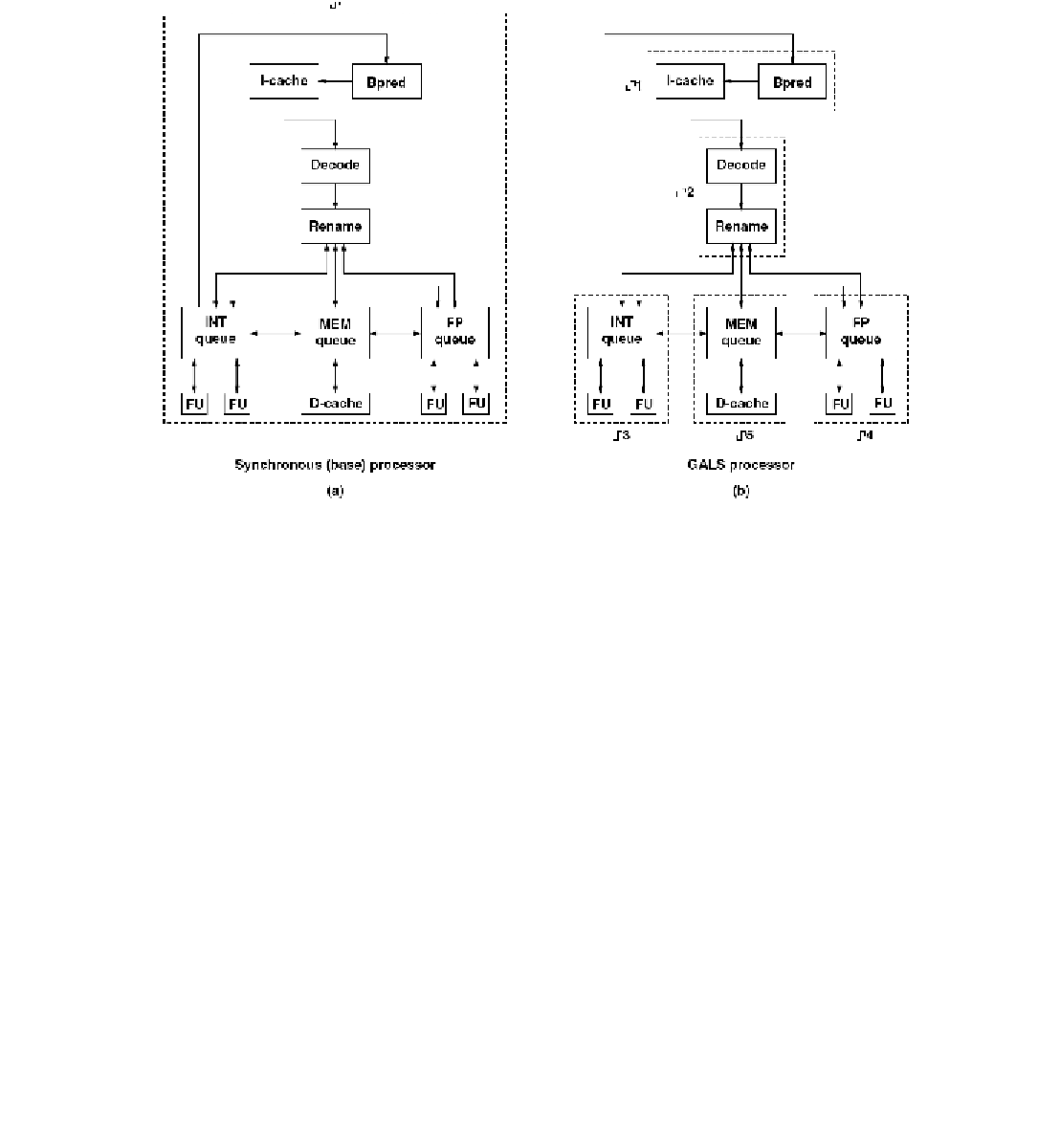

FIGURE 3.5:

Synchronous versus GALS processor. Reproduced from [

117

]. Copyright 2002 IEEE.

clock domains, the drop in performance ranges between 5% and 15%, while power consumption

is reduced by 10% on the average. Thus, fine-grained voltage scaling allows GALS to match

or exceed the power efficiency of fully synchronous approaches.

In a similar timeframe, research from Albonesi's group also explored DVFS opportunities

in MCD processors [

199

,

200

]. Similar to the Iyer and Marculescu MCD division of the CPU

(Figure 3.5), Semeraro et al. divide the processor into five domains: Front end, Integer, Floating

point, Load/Store, and External (Main Memory). The division is shown in Figure 3.6 along

with the relevant clock parameters. The domains interface via queues.

The work by Semerao et al. primarily focused on the control policies by which (

V

,

f

) settings could be optimized for such microarchitectures. Their early work used offline

scheduling to accomplish good (

V

,

f

) settings, but subsequent work explored control-theoretic

approaches for managing MCD processors.

Offline approach

: Semeraro et al. use an offline approach in [

200

] to select the times and

frequency values for DVFS in an application. The application is executed (at maximum speed)

in a simulator that creates an event trace. The events correspond to primitive operations in

the processor (for example, for a load instruction: fetch, dispatch, address calculation, memory

access, and commit events are traced). The events are connected with resource constraints and

Search WWH ::

Custom Search