Information Technology Reference

In-Depth Information

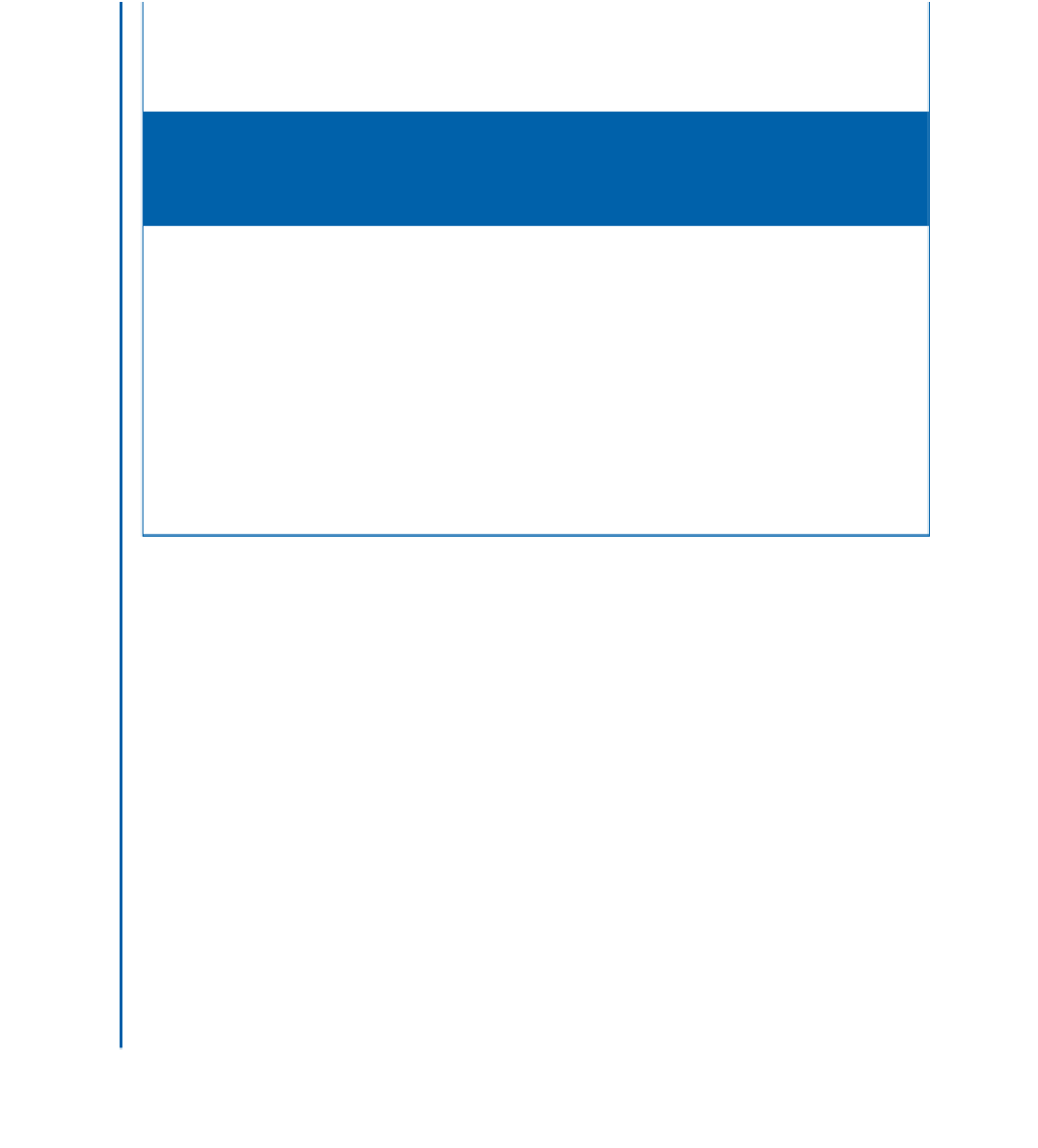

TABLE 2.1:

This Table Summarize Parameterized Equations That Express the Capacitance for

Different Key Nodes of the Cache Array in Figure 2.2. C

diff

C

gate

,andC

metal

refer to the capacitance

of diffusion, gate and metal regions respectively. Adapted from [

38

].

Node

Capacitance Equation

Regfile Wordline Capacitance

=

C

diff

(

WordLineDriver

)

+

C

gate

(

CellAccess

)

∗

NumBitlines

+

C

metal

∗

WordLineLength

Regfile Bitline Capacitance

=

C

diff

(

PreCharge

)

+

C

diff

(

CellAccess

)

∗

NumW dlines

+

C

metal

∗

BLLength

CAM Tagline Capacitance

=

C

gate

(

CompareEn

)

∗

NumberTags

+

C

diff

(

CompareDriver

)

+

C

metal

∗

TLLength

CAM Matchline Capacitance

=

2

∗

C

diff

(

CompareEn

)

∗

TagSize

+

C

diff

(

MatchPreCharge

)

+

C

diff

(

MatchOR

)

+

C

metal

*

MLLength

ResultBus Capacitance

=

0.5

∗

C

metal

∗

(

NumALU

∗

ALUHeight

)

+

C

metal

∗

(

RegfileHeight

)

model in which constants are subsumed into a clearer form, expressing

I

leak

as

10

−

V

T

/

S

T

=

N

·

K

design

·

k

tech

·

.

From this,

P

leak

can be expressed as

P

static

=

V

CC

·

N

·

k

design

·

I

leak

.

The key insight here is that many detailed aspects of the circuit design choices can be abstracted

into the

k

design

factor seen in these equations. The

k

design

parameter in some sense represents the

degree of “stacking” seen by transistors in different types of circuit designs (e.g., array structures

versus static logic, etc.). The HotLeakage simulation framework [

247

] builds on Butts/Sohi

analytics to provide a simulation package for leakage energy.

To see how Butts and Sohi arrived at the simplified formulas, we start with the Berkeley

Predictive Model (BSIM3V3.2) formula that gives subthreshold leakage current as

1

t

−

V

T

−

e

−

V

ds

V

gs

V

off

I

Dsub

=

I

s0

·

−

·

e

v

n

·

v

t

Search WWH ::

Custom Search