Information Technology Reference

In-Depth Information

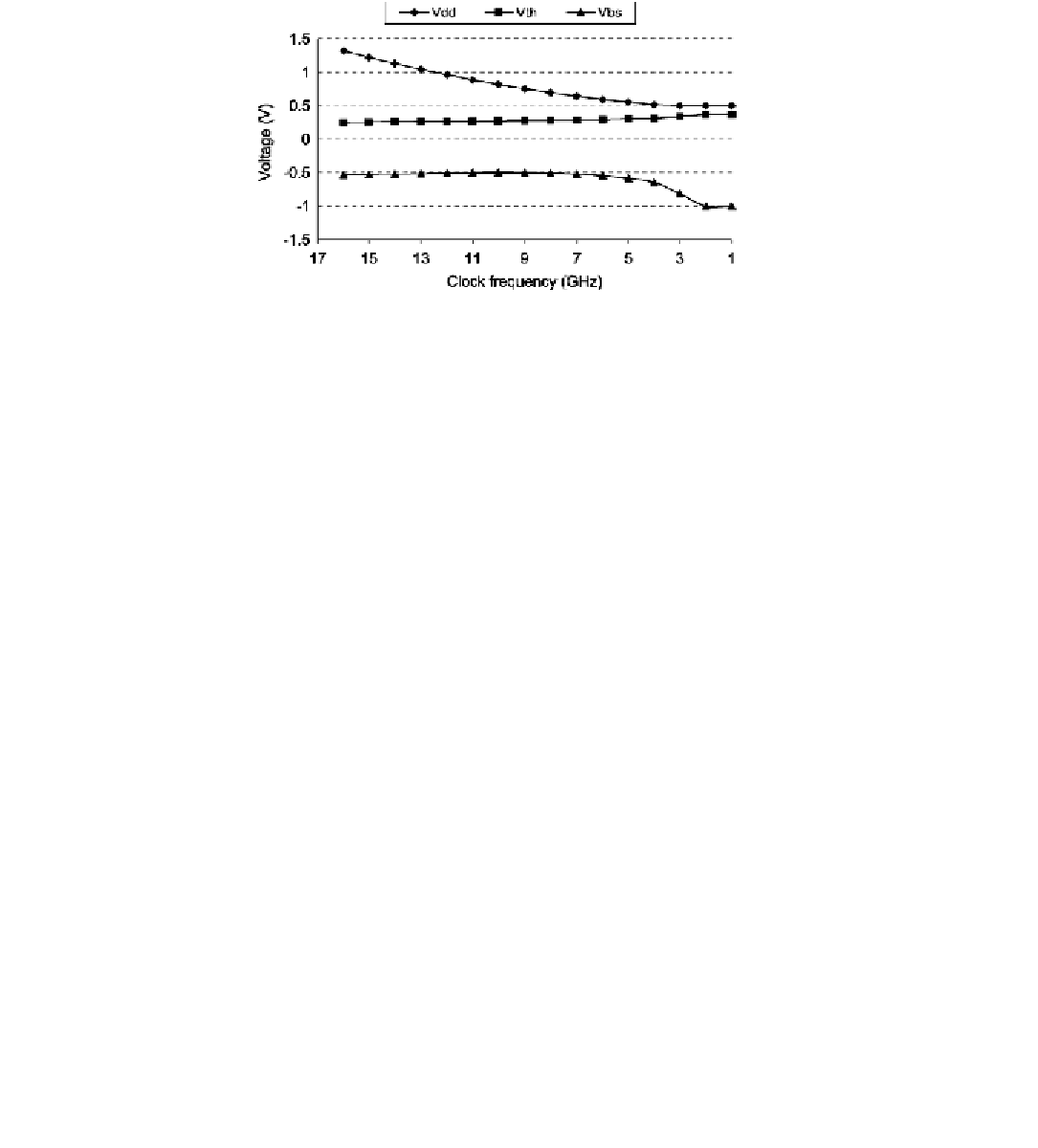

FIGURE 5.19:

Combined DVS and ABB for an embedded processor with hard real-time constraints.

Reproduced from [

231

]. Copyright 2005 IEEE.

Finally, Yan, Luo, and Jha study the application of combined DVS and ABB in

heterogeneous distributed real-time embedded systems [

231

]. In analogy to the work

of Martin et al., they determine the lowest frequency of operation that can satisfy the

real-time constraints of an embedded system using the worst-case analysis. In contrast

to the previous work, the deadlines are known and are hard real time.

Given the required operation frequencies, Yan et al. show that both

V

dd

and

V

T

have to scale to obtain the minimum power across the range of frequencies for a 70 nm

technology ( Figure 5.19). Initially,

V

dd

is scaled as this yields the most power reduction

for the given frequencies. However, at some point

V

dd

scaling reduces dynamic power

to the point where leakage starts to dominate, thus triggering ABB (scaling the body-

to-source bias

V

bs

). Yan et al. conclude their study by presenting a heuristic on-line

algorithm that can estimate the proper

V

dd

and

V

bs

for a list of tasks with a slack in

their execution schedule.

5.4.2 Static Approaches

In the static, multiple-

V

T

approaches, transistors on the same die are manufactured as either

high-

V

T

or low-

V

T

(by varying the channel-doping profile, or the oxide thickness, or the channel

length). These are referred to as multi-threshold voltage CMOS (MTCMOS) technologies

with the appropriate libraries providing devices with different

V

T

. The designer or architect

selects where the high-

V

T

or low-

V

T

devices go at design time and the chip is manufactured

accordingly. There are two major design methodologies in using multiple threshold voltages.

The first methodology is to use

low

-

V

T

devices (high-performance, high-leakage)

in the performance-critical paths of a design and use

high-V

T

(lower-performance,

Search WWH ::

Custom Search