Information Technology Reference

In-Depth Information

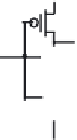

1V

2-State

FSM

External

Signal (every 512c)

Cache

Line

W/L

W/L

Decaying

Cell

(6T)

Power Line

W/L

4T

0.3V

Gating

Transistor

Low Leak

Inverter

Low Leak

Supply Regulator

FIGURE 5.16:

Decaying 4T timer for a hybrid decay

+

drowsy policy. Reproduced from [

129

].

Copyright 2005 IEEE.

☞

decaying 4T timers

: A 4T DRAM cell can be used as a cheap temperature-sensitive

timer [

128

]. The time it takes to discharge because of leakage is a measure of temperature.

The timer in the temperature-adaptive hybrid technique is based on the same idea: the

decay interval of each cache line is regulated by the decay of a 4T cell.

A simplified timing mechanism that sets a cache line in drowsy or decay mode is

depicted in Figure 5.16. Implemented adjacent to each cache line, this mechanism adapts

the decay interval to the temperature of the line's immediate surrounding area. The drowsy

interval is fixed and is counted by a single-bit local counter. Accessing a line charges the

4T cell—i.e., resets the timer. As long as the 4T holds a “1” the cache line is connected to

ground. If, however, the 4T is left unaccessed for a long period, it decays and gates the cache

line via a low leak sleep transistor. As soon as the line is accessed again, the 4T reinstates

the connection to ground. Additional hardware is needed to synchronize the decay of the

4T with the clock and cache operations.

5.3.5 Reliability

Finally, the different leakage-reduction techniques can have a very different reliability behavior

compared to a standard cache. Degalahal, Vijaykrishnan, Kandemir, and Irwin examine cache

decay and drowsy caches from a reliability perspective [

63

] and conclude that decay enhances

reliability, whereas the drowsy mode makes caches more susceptible to soft errors.

Technology scaling fundamentally affects the reliability of devices, increasing the rate

of soft (transient) errors. Such errors are primarily caused by external radiation such as alpha

particle or high-energy neutron strikes but it is the physical characteristics of the devices that

determine whether transient errors occur during these strikes.

Search WWH ::

Custom Search