Information Technology Reference

In-Depth Information

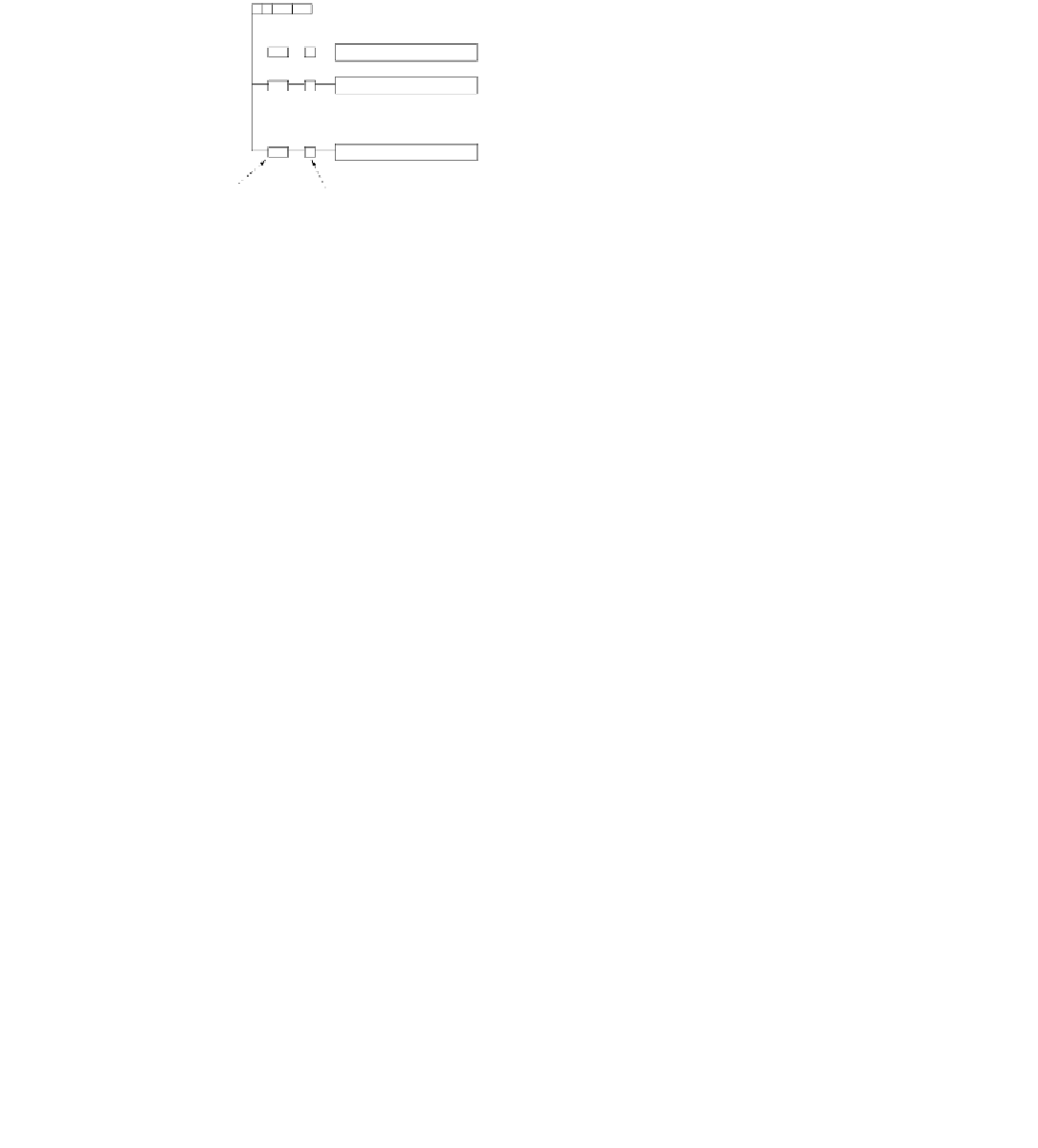

GLOBAL COUNTER

GLOBAL COUNTER

LOCAL 2-BIT COUNTERS

VALID BIT

V

CACHE-LINE (DATA + TAG)

V

CACHE-LINE (DATA + TAG)

WRD

TICK

PULSE

V

CACHE-LINE (DATA + TAG)

V

CACHE-LINE (DATA + TAG)

WRD

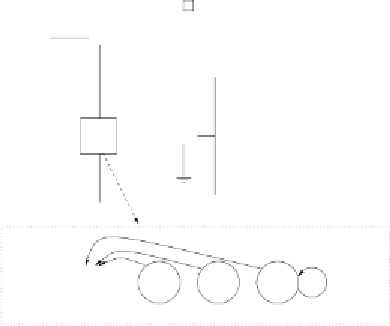

ROW

DECODERS

CASCADED

TICK

PULSE

B

B

BB

V

V

T

V

CACHE-LINE (DATA + TAG)

FSM

M

M

WRD

V

V

g

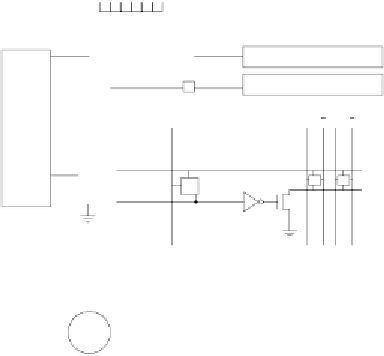

2-bit

Counter

Power-Off

LOCAL 2-BIT COUNTERS

VALID BIT

RESET

ALWAYS POWERED

SWITCHED POWER

WRD

WRD

WRD

S1

S0

0

1

1

1

1

0

T/

PowerOff

0

0

T

T

T

State Diagram for 2-bit (S1,S0), saturating, Gray-code counter with two inputs (WRD, T)

FIGURE 5.6:

High-level view of the hierarchical counters. Reproduced from [

127

]. Copyright 2001

IEEE.

What makes this scheme viable, though, is that its effectiveness remains the same as if

we had full cycle counters in every cache line.

9

In other words, it does not matter whether we

count in cycles or in

thousands

of cycles when we are measuring large decay intervals.

The use of a global cycle counter also offers another advantage. It allows the flexibility to

adjust the decay interval at a central, global, point. The local cache line counters measure idle

time but they do not explicitly compare to the decay interval. Instead, when they reach their

last state they consider the cache line to be dead and “activate” (turn

off

) the sleep transistor.

Thus, the only way to adjust the decay interval is to control the period of the global beat (which

ticks the local counters) given by the global counter.

Switching off power to a cache line has implications for the way the cache works. The

first access to a powered-off cache line results in a miss (since data and tag are lost without

power). The miss resets the cache line counter and restores power. Since the cache frame is

written after the miss, the time to fetch the data from the lower part of the cache hierarchy is

typically sufficient for the memory cells to stabilize after power is restored and accept the write.

☞

decaying dirty data

: In a non-state-preserving technique, one has to address the problem

of dirty data in a writeback cache. Decaying a dirty cache line necessitates a writeback. If the

global counter signal is distributed in parallel to all the local counters, there is a chance that

multiple lines will need to be written back at the same time if they all decay at the same global

beat. This would choke the cache, in terms of access bandwidth requirements. To avoid this

9

Even 2-bit local counters—very coarse time resolution—approximates the effect of full resolution.

Search WWH ::

Custom Search