Global Positioning System Reference

In-Depth Information

Optional

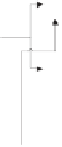

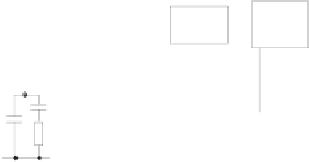

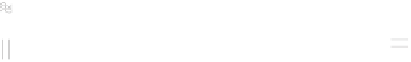

filter

LNA_OUT

MIX_IN

VAGC

AGC_DIS

AGC

Controller

IF Filter

∼

-45°

MAG

ADC

LNA

SIGN

+45

°

Buffer

I

Q

LNA_IN

CLK_OUT

Clock

select

FREF2

FREF1

FREF0

Quadrature

÷2

Feedback

Divider

Chip

control

VCO

∼

RX_ENB

OSC_ENB

RVI

Phase/

Frequency

Detector

Reference

buffer/

oscillator

Reference

Divider

VTUNE

XTAL1

XTAL2

FIGURE 4.8. Block diagram of the SE4110L front-end ASIC. Reproduced with permission

of SiGe Semiconductor, Inc.

Based on the discussion within the chapter, the underlying design of the compo-

nent should be somewhat familiar. A single-frequency translation stage is utilized

along automatic gain control functionality to support multiple bit sampling.

It is quite impressive to see the level of integration within such a component.

It utilizes a traditional antenna input (although a passive antenna can be used

with an internal LNA with noise figure of less than 2

5 dB) and provides 2-bit

digital samples supporting a number of different clock frequencies for a variety

of applications. This particular part is only 4

.

4 mm and draws less than 10 mA

from a nominal 2.7-3.3 V supply. Such integration is even more impressive when

one considers the gain required for processing the received signal power of the

GPS and potential feedback issues.

Such development even further facilitates the wide scale deployment of satellite

navigation technology at a relatively low cost.

The ASIC-based front end is just one of multiple options for converting the sig-

nal in space to a digital format suitable for the software based signal processing.

The goal of this chapter is to provide some insight into the source of that data.

×

Search WWH ::

Custom Search