Information Technology Reference

In-Depth Information

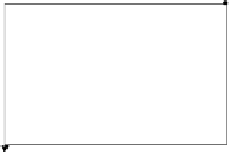

sondern als ein zeitsequentiell arbeitender

2-Port-Speicher

. Tatsächlich ist das ein 1-

Port-Speicher, auf den man zeitversetzt zugreift, um Befehle lesen bzw. Daten lesen

oder schreiben zu können. Als Konsequenz sind für die Bearbeitung eines auf ein

Datum zugreifenden Befehls statt eines Taktschrittes zwei Taktschritte erforderlich.

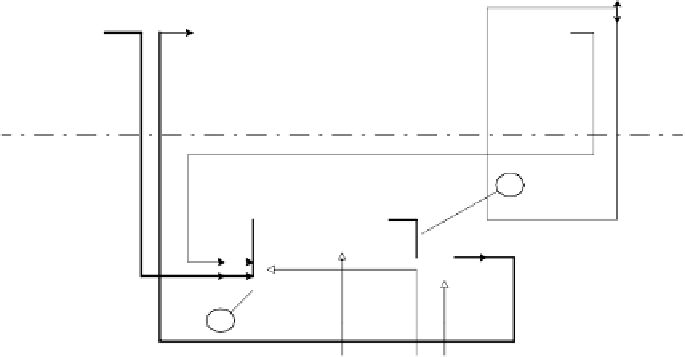

M

1

M

4

AC

+

SP

ALU

+1

CC

1

M

5

M

2

Befehlsdecoder

M

3

b

Haupt-

speicher

(ME)

M

6

c

a

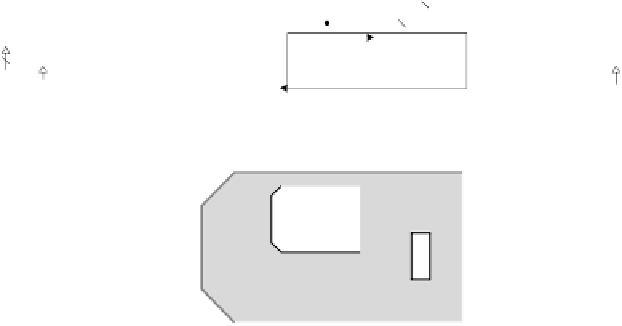

Bild 2.15.

Registertransferstruktur eines Prozessors mit 1-Adressarchitektur, der einen gemeinsa-

men Speicher für Daten und Befehle verwendet

Zunächst wird der mit a markierte Multiplexer M

6

in der Weise gesteuert, dass die-

ser den Inhalt des Befehlszählers PC auf den Hauptspeicher durchschaltet (dick

gezeichnete Verbindung) und den so gelesenen Befehl über die mit b markierte Ver-

bindung zum

Instruktionsregister IR

(

instruction register

) überträgt. Mit dem Takt

wird der als nächstes auszuführende Befehl in das Instruktionsregister IR geladen

und über die mit c markierte Verbindung, genauso wie von dem in Bild 2.10 darge-

stellten Prozessor, weiterverarbeitet. In dieser zweiten Verarbeitungsphase schaltet

außerdem der Multiplexer M

6

so, dass der Hauptspeicher die Funktion des Daten-

speichers übernimmt, und zwar solange, bis der Befehl vollständig verarbeitet

wurde.

Bemerkung. Die Begriffe Harvard-Architektur und von Neumann-Architektur sind nicht unum-

stritten. Einerseits hat von Neumann in seinem berühmten Memorandum über den sog. Stored-Pro-

gram-Computer nicht ausgeschlossen, dass Befehle und Daten in getrennten Speichern gehalten

werden können (siehe [98]), demnach eine Harvard-Architektur gleichzeitig eine von-Neumann-

Architektur ist. Andererseits würdigt der Begriff der von-Neumann-Architektur nicht, dass in dem

Team, in dem die Idee des Stored-Programm-Computers entwickelt wurde, neben von Neumann

maßgeblich die Computerpioniere Eckert und Mauchly tätig gewesen sind [58].

Search WWH ::

Custom Search