Information Technology Reference

In-Depth Information

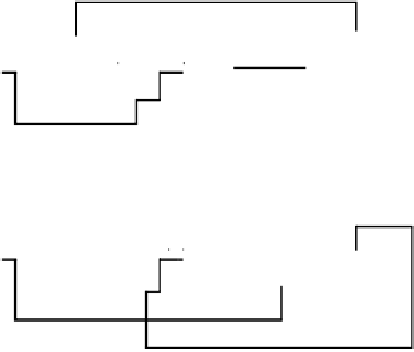

Befehlszähler

a

Daten-

speicher

Register-

speicher

Befehlscode

ALU

a

Befehlszähler

c

Register-

speicher

Befehlscode

ALU

Daten-

speicher

a

b

b

Befehlszähler

AC

IX

IX

ALU

Daten-

speicher

b

Befehlscode

c

a

Befehlszähler

b

Daten-

speicher

TOS

TOS

-1

ALU

a

d

Befehlscode

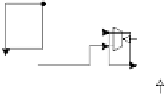

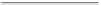

Bild 2.9.

Datenwerke von Prozessoren mit unterschiedlichen Architekturen.

a

3-Adressdatenwerk,

b

2-Adressdatenwerk,

c

1-Adressdatenwerk,

d

0-Adressdatenwerk

2-Adressarchitektur

In Bild 2.9b stellt das Datenwerk eines Prozessors mit 2-Adressarchitektur dar. Der

Registerspeicher verfügt über zwei

Ports

über die zeitgleich zwei Lesezugriffe oder

ein Lese- und ein Schreibzugriff durchgeführt werden können. Die bei dyadischen

Operationen notwendigen drei Zugriffe werden hier zeitsequentiell ausgeführt: Im

ersten Schritt werden die zu verarbeitenden Operanden gelesen, in der ALU mitein-

ander verknüpft und das Ergebnis in dem für Programmierer unsichtbaren techni-

schen Register OP abgelegt. Im zweiten Schritt wird das dort zwischengespeicherte

Search WWH ::

Custom Search