Information Technology Reference

In-Depth Information

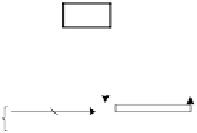

Zunächst trennt man von der im Befehl codierten virtuellen Registeradresse die oberen beiden Bits

ab, um so zu unterscheiden, ob ein globales (in diesem Fall sind die oberen beiden Bits gleich 0)

oder ein lokales Register adressiert werden soll. Bei einem Zugriff auf ein globales Register wird

vom Multiplexer eine fünf Bit breite Konstante durchgeschaltet und anschließend mit den unteren

drei Bits zu einer realen Registeradresse zusammengesetzt. Das acht Bit breite Ergebnis liegt dabei

im Adressbereich 10000000

2

bis 10000111

2

.

CWP

0

virtuelle Registeradresse

reale Registeradresse

4

2

Register-

speicher

5

+

8

4

5

3

Bild 2.8.

Registertransferschaltung zur Umwandlung einer codierten virtuellen 5-Bit-Registera-

dresse in eine reale 8-Bit-Registeradresse (ähnlich wie im UltraSPARC IIIi von Sun [173])

Falls der Zugriff sich auf ein lokales Register bezieht, ist die Umwandlung komplizierter. Im Prin-

zip wird hierbei der Inhalt des CWP mit 16 multipliziert und dadurch die reale Registeradresse des

zu verwendenden Registerfensters berechnet. Durch Addition mit der im Befehl codierten virtuel-

len Registeradresse lässt sich daraus schließlich die reale Registeradresse erzeugen. Genau dies ist

auf geschickte Weise in Bild 2.8 implementiert.

2.1.6 Datenwerke und Datenregister

Die meisten Merkmale der Registertransferschaltung in Bild 2.7 lassen sich auch auf

andere Art und Weise realisieren, und zwar ohne hierbei eine verminderte Leis-

tungsfähigkeit in Kauf nehmen zu müssen. Alle Varianten zu beschreiben, ist wegen

der großen Vielfalt jedoch nicht möglich, weshalb im Folgenden grundsätzliche

Architekturprinzipien diskutiert werden, die den Datenwerken von Prozessoren

zuzuordnen sind. Bild 2.9 stellt von oben nach unten die aufs Wesentliche reduzier-

ten Datenwerke von Prozessoren dar, die eine 3-, 2-, 1- bzw. 0-Adressarchitekturen

aufweisen. Die Registertransferschaltungen unterscheiden sich vor allem in den

Datenregistern, die in Bild 2.9a und 2.9b als 3- bzw. 2-Port-Registerspeicher, in Bild

2.9c als Akkumulator mit Indexregister und in Bild 2.9d als Stapel realisiert sind

(siehe hierzu auch Abschnitt 1.3.2).

3-Adressarchitektur

Das Datenwerk in Bild 2.9a entspricht nach Vereinfachung dem, was in Bild 2.7 dar-

gestellt ist und dort bereits detailliert beschrieben wurde. Der darin enthaltene

3-

Port-Registerspeicher

erlaubt das gleichzeitige Lesen von drei Operanden oder

alternativ das Lesen von zwei Operanden und das Schreiben von einem Ergebnis.

Zu Vergleichszwecken sind einige Verbindungen in Bild 2.9a dick gezeichnet. Sie

werden bei Zugriffen auf den Datenspeicher benötigt, wobei die mit a markierte

Verbindung bei einem Ladebefehl vom Daten- zum Registerspeicher und bei einem

Speicherebefehl vom Register- zum Datenspeicher erforderlich ist.

Search WWH ::

Custom Search