Information Technology Reference

In-Depth Information

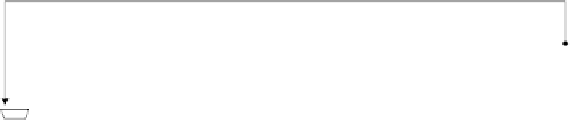

Neben dem Operationscode ist in Sprungbefehlen also nur noch die Sprungdistanz

codiert. Insbesondere ist es nicht möglich, eine Registeradresse in bedingten

Sprungbefehlen anzugeben, die jedoch benötigt wird, um auf das die Bedingungs-

größe enthaltende Register zuzugreifen. Deshalb werden in Bild 2.7 die Bedin-

gungsgroßen nicht direkt vom Decoder ausgewertet, sondern zunächst im

Bedin-

gungsregister CC

(

condition code

, im Bild durch c markiert), das bei einem Operan-

denvergleich entsprechend aller von einem Prozessor auswertbaren Relationen

gesetzt und dabei ebenfalls implizit adressiert wird (siehe hierzu Abschnitt 1.1.7).

b

a

d

+

≥

3n

0

+1

Befehls-

speicher

Register-

speicher

Daten-

speicher

ALU

n

CC

c

Befehlsdecoder

Bild 2.7.

Registertransferschaltung eines sequentiell arbeitenden Prozessors, der ein Bedingungsre-

gister besitzt und befehlszählerrelative Sprünge ausführen kann

Ganz ähnlich kann verfahren werden, um die Rücksprungadresse von Unterpro-

grammaufrufen zu sichern. Zur impliziten Adressierung des bei einem Unterpro-

grammaufrufs zu verwendenden Registers wird über den mit d markierten Multiple-

xer eine Konstante auf den Registerspeicher durchgeschaltet, die festgelegt, in wel-

chem Register die Rücksprungadresse gesichert werden soll (hier in r0). Nachteil

dieses Verfahrens ist, dass bei geschachtelten Unterprogrammaufrufen eine mögli-

cherweise bereits gesicherte Rücksprungadresse überschrieben wird, was sich

jedoch verhindern lässt, indem der Inhalt des entsprechenden Registers vor jedem

Unterprogrammaufruf gesichert und nach jedem Unterprogrammaufruf wieder her-

gestellt wird (trotz dieses Nachteils ist das Verfahren weit verbreitet und wird z.B.

im Alpha 21364 von Compaq [25, 28], im PowerPC 970 von IBM [67] und anderen

Prozessoren verwendet).

Bemerkung. Wie in Abschnitt 1.4.2 beschrieben wurde, ist es möglich, einen Registerspeicher

auch nichtlinear adressierbar zu realisieren. Zum Beispiel verfügt der UltraSPARC IIIi von Sun

[173] über 128 lokale und acht sichtbare globale Register. Ein wahlfreier Zugriff auf alle Register

erfordert somit wenigstens acht Bit breite Adressen. Tatsächlich sind in den Befehlen jedoch nur

fünf Bit breite Adressen codiert, mit denen der Zugriff auf acht

globale

und maximal 24

lokale

Register möglich ist.

Damit trotzdem alle 128 lokalen Register angesprochen werden können, ist der Registerspeicher

zusätzlich in

Fenstern

organisiert, von denen eines durch den sog. CWP (current window pointer)

ausgewählt wird. Er ist fünf Bit breit, enthält beim UltraSPARC III jedoch nur drei relevante Bits.

Bei einem Zugriff auf ein Register, wird die im Befehl codierte Adresse und der Inhalt des CWP zu

einer realen Registeradresse umgeformt. Wie dies prinzipiell geschieht, ist in Bild 2.8 als Register-

transferschaltung andeutungsweise dargestellt.

Search WWH ::

Custom Search