Information Technology Reference

In-Depth Information

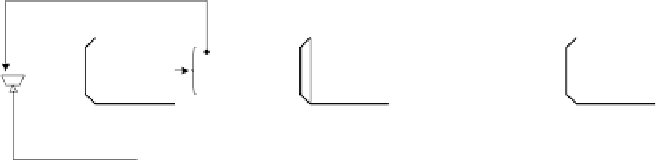

Arithmetische und logische Operationen lassen sich in ähnlicher Weise wie von der

in Bild 2.2 dargestellten Struktur verarbeiten, nur dass das von der ALU erzeugte

Ergebnis hier über einen vom Befehlsdecoder gesteuerten Multiplexer in den Regis-

terspeicher geschrieben wird. Den Multiplexer benötigt man, um den angeschlosse-

nen Registerport alternativ mit dem Ausgang der ALU oder mit dem Datenspeicher,

in diesem Fall bidirektional, zu verbinden (dick gezeichneter und mit b markierter

Bus). So ist es möglich, Inhalte aus dem Daten- in den Registerspeicher oder umge-

kehrt aus dem Register- in den Datenspeicher zu transportieren. Die Datenrichtung

wird dabei vom Befehlsdecoder vorgegeben, der, vom auszuführenden Befehl

abhängig, sowohl den Register- als auch den Datenspeicher anweist, jeweils alter-

nierend als Quelle oder Senke zu fungieren.

Die Adressierung des Datenspeichers geschieht dabei auf eine zu Bild 2.2 vergleich-

bare Weise, und zwar, indem die im Befehl codierte direkte Adresse auf den Daten-

speicher geführt wird (über den mit a markierten Bus). Statt der vormals drei Daten-

speicheradressen muss nun jedoch nur eine Datenspeicheradresse im Befehl angege-

ben sein. Die Befehle lassen sich also kompakter codieren als für den in Bild 2.2

dargestellten Prozessor.

b

a

+1

Befehls-

speicher

Register-

speicher

Daten-

speicher

ALU

N

n

Befehlsdecoder

Bild 2.4.

Registertransferschaltung eines einfachen sequentiell arbeitenden Prozessors, mit 3-Port-

Register- und 1-Port-Datenspeicher

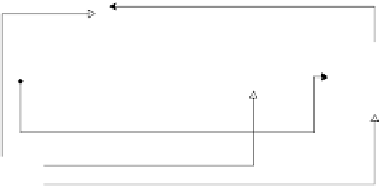

Es ist wichtig auf Folgendes hinzuweisen: Der für die Datenspeicheradresse vorge-

sehene Platz im Befehlscode ist für andere Zwecke verwendbar, wenn nicht auf den

Datenspeicher zugegriffen werden muss. Im Bild wird dies genutzt, um statt der N-

Bit-Datenspeicheradresse eine der drei n-Bit-Registeradressen zu codieren. Es

wurde darauf verzichtet, die zweite Registeradresse ebenfalls in dem N Bit breiten

Feld für die Datenspeicheradresse zu codieren, da die Struktur in Bild 2.4 dadurch

etwas unübersichtlicher geworden wäre. Tatsächlich ließen sich die Befehle auf

diese Weise jedoch etwas kompakter codieren, weil nämlich die zweite Registera-

dresse in Befehlen, die auf den Datenspeicher zugreifen, nicht benötigt wird. Für die

folgenden Betrachtungen ist dies ohne Bedeutung.

2.1.4 Datenadressierung

Der in Bild 2.4 dargestellte Prozessor kann direkt auf den Register- oder Datenspei-

cher zugreifen, ist jedoch noch nicht imstande, unmittelbare Operanden zu verarbei-

ten oder indirekt auf den Datenspeicher zuzugreifen. Beides lässt sich durch gering-

Search WWH ::

Custom Search