Information Technology Reference

In-Depth Information

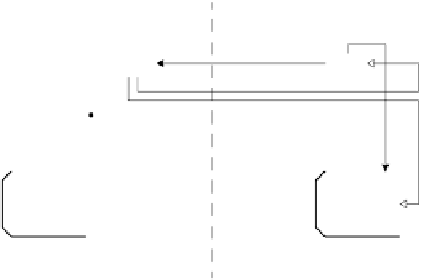

Befehle drei Adressen erfordern, aber in allen Befehlen drei Felder enthalten sind.

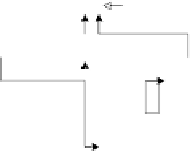

Auf welche Weise sich die angedeuteten Probleme lösen lassen, wird im nächsten

Abschnitt beschrieben. Zuvor soll jedoch noch gezeigt werden, dass die Register-

transferschaltung in Bild 2.2 tatsächlich der theoretischen Struktur in Bild 2.1 ent-

spricht. Hierzu wurde in Bild 2.3 die Registertransferschaltung in der Weise umge-

zeichnet, dass Leiteinheit und Dateneinheit darin durch Ovale vergleichbar mit Bild

2.1 eingegrenzt sind. Die Steuerung des Datenwerks geschieht durch die unteren

fünf Signalbündel, die von der Leit- zur Dateneinheit geführt sind. Das darüber dar-

gestellte Signal dient der Steuerung des Leitwerks durch das Datenwerk. Der Leit-

werkszustand ist im Befehlszähler gespeichert, dessen Inhalt von der Leiteinheit

schrittweise verändert werden kann. Die Dateneinheit besitzt entsprechend der

gemachten Vorgaben keine solche Rückkopplung.

Leitwerk

Datenwerk

Befehlsdecoder

ALU

PC

+

1

Befehls-

speicher

Daten-

speicher

unveränderlich

veränderlich

(Datenzustand)

Bild 2.3.

Entsprechend der theoretischen Struktur in Bild 2.1 umgezeichnete Registertransferstruk-

tur des Prozessors, der in Bild 2.2 dargestellt ist

2.1.3 Speicherung

Ein Prozessor entsprechend der Registertransferstruktur aus Bild 2.2 wird man vor

allem wegen des aufwendigen 3-Port-Datenspeichers nicht wirklich realisieren, da

die heute normalerweise verwendeten Speichermodule nur über einen einzelnen

Port für Schreib- und Lesezugriffe verfügen. Eine direkte Lösung dieser Problema-

tik besteht darin, den Datenspeicher zeitsequentiell anzusteuern, also auf Operanden

und Ergebnis nacheinander zuzugreifen. Als Nachteil muss jedoch in Kauf genom-

men werden, dass die Ausführungsgeschwindigkeit, mit der sich die Befehle verar-

beiten lassen, deutlich geringer ausfällt, als wenn auf die Operanden und das Ergeb-

nis parallel zugegriffen wird.

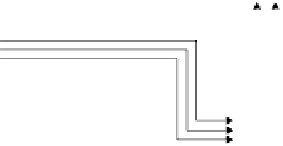

Eleganter ist es, wenn man den Datenspeicher durch einen

Registerspeicher

ersetzt,

der eine geringe Kapazität aufweist und sich daher leicht mit drei Ports realisieren

lässt. Um große Datenmengen speichern zu können, wird dem 3-Port-Register-

außerdem ein

1-Port-Datenspeicher

großer Kapazität zur Seite gestellt. In Bild 2.4

ist ein Prozessor mit

Lade-Speichere-Architektur

dargestellt, der direkt aus der

Registertransferschaltung entsprechend Bild 2.2 hergeleitet wurde (zur Lade-Spei-

chere-Architektur siehe Abschnitt 1.3.2).

Search WWH ::

Custom Search