Information Technology Reference

In-Depth Information

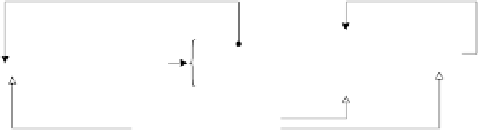

die Operanden gelesen sind, kommt die Operation in der sog.

Arithmetisch-Logi-

schen-Einheit

(

arithmetic-logical-unit

,

ALU

) zur Ausführung. Das Verknüpfungser-

gebnis wird schließlich, vom Befehl abhängig, ggf. in den Datenspeicher geschrie-

ben, und zwar gesteuert vom

Befehlsdecoder

.

Die Bearbeitung eines Befehls ist jedoch noch nicht beendet. Neben dem Verknüp-

fungsergebnis generiert die ALU nämlich noch ein vom Befehlsdecoder optional

auswertbares Bedingungsergebnis. Abhängig oder unabhängig von diesem Signal

wird gesteuert, ob sich die in den Befehlszähler zu ladende Adresse des nächsten

auszuführenden Befehls dadurch ergibt, dass die aktuelle Befehlsadresse inkremen-

tiert, also nicht verzweigt wird, oder dadurch, dass die im Befehl codierte Ziel-

adresse verwendet, also verzweigt wird.

+1

Befehls-

speicher

Daten-

speicher

ALU

Befehlsdecoder

Bild 2.2.

Registertransferstruktur eines einfachen Prozessors

Bis zu diesem Zeitpunkt ist weder der Befehlszähler, noch der Inhalt des Datenspei-

chers modifiziert worden. In den normalerweise synchron arbeitenden Prozessoren

geschieht das mit der nächsten steigenden, fallenden oder einer beliebigen Takt-

flanke. Dies ist essentiell für die Funktionsweise eines synchron arbeitenden Prozes-

sors, da es sonst z.B. möglich wäre, dass der Inhalt des Befehlszählers sich ändert,

bevor der Zugriff auf den Befehlsspeicher abgeschlossen ist.

Die in Bild 2.2 dargestellte Registertransferschaltung erlaubt einige Rückschlüsse

auf das dem Prozessor zugrunde liegende Programmiermodell. Aus der Datenspei-

cheransteuerung kann geschlossen werden, dass es sich um eine 3-

Adressarchitektur

handelt, die Befehle fester Breite verarbeitet. Sowohl auf den Daten- als auch den

Befehlsspeicher wird direkt zugegriffen. Andere Adressierungsarten, insbesondere

die indirekte oder unmittelbare Adressierung finden keine Unterstützung. Bedingte

Sprungbefehle verzweigen abhängig von einem Bedingungsergebnis, das entweder

im Datenspeicher abgelegt sein muss oder mit dem Sprungbefehl erzeugt wird. Im

Befehl sind jeweils die Adressen der auszuwertenden Operanden und das potentielle

Sprungziel codiert. Da der Inhalt des Befehlszählers nicht sicherbar ist, lassen sich

keine Unterprogrammaufrufe durchführen. Welche Befehle im Detail verarbeitbar

sind, ist der Registertransferschaltung in Bild 2.2 nicht zu entnehmen. Um diese

Information zu erhalten, müsste man den Befehlsdecoder analysieren, der die Ope-

rationscodes in den Befehlen, u.a. in ein Steuersignalbündel für die ALU umwan-

delt, in der alle arithmetisch-logischen Befehle ausgeführt werden.

Der Speicherbedarf eines Programms für den im Bild 2.2 dargestellten Prozessor ist

aller Voraussicht nach sehr hoch, und zwar deshalb, weil bei Adressraumgrößen von

heute wenigstens 4 GWorten 32 Bit breite Adressen erforderlich sind. Ein Befehl ist

somit wenigstens 96 Bit breit. Nachteilig wirkt sich hier auch aus, dass nicht alle

Search WWH ::

Custom Search