Information Technology Reference

In-Depth Information

ersetzt), reicht es aus, nur einen einzelnen Operanden dyadischer Operationen

unmittelbar adressieren zu können und im Befehl ein einzelnes Adressmodusbit vor-

zusehen. Die meisten Prozessoren erlauben die unmittelbare Adressierung des zwei-

ten Operanden, was für nichtkommutative Operationen, wie die Subtraktion oder

die Division, eine Einschränkung darstellt, und zwar immer dann, wenn der erste

Operand eine unmittelbar adressierte Konstante sein soll. Gegebenenfalls ist ein

zusätzlicher Befehl erforderlich, um die jeweils gewünschte Wirkung zu erzielen.

So kann die Subtraktion 1

-x

z.B. durch die Subtraktion

E-x

nachgebildet werden,

wobei

E

ein Register ist, das zuvor mit Eins initialisiert wurde.

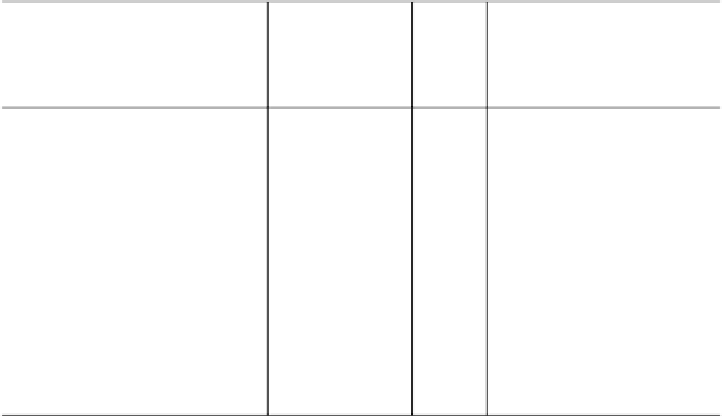

Tabelle 1.3.

Registerspeichergrößen von Prozessoren mit 3-Adressarchitektur

Anzahl allgemeiner

Register

Bitbreite

Direkt

zugreifbar

Register-

breite

Register-

adressen

unmittelbare

Operanden

Prozessor/Architektur (Hersteller)

Gesamt

Befehl

Alpha 21364 (Compaq) [25, 28]

32

32

64 Bit

5 Bit

8 Bit

32 Bit

Am29000 (AMD) [1]

192

192

32 Bit

8 Bit

8 Bit

32 Bit

32 Bit

a

ARM7TDMI (ARM) [10]

16

16

32 Bit

4 Bit

8 Bit

-

b

-

b

Crusoe TM5800 (Transmeta) [187]

64

64

32 Bit

6 Bit

pa-8700 (HP) [90]

32

32

64 Bit

5 Bit

11 Bit

32 Bit

8 Bit

c

41 Bit

d

Itanium 2 (Intel, HP) [75, 78]

128

128

64 Bit

7 Bit

MC88100 (Motorola) [122]

32

32

32 Bit

5 Bit

16 Bit

32 Bit

MIPS64 20Kc (MIPS) [106]

32

32

64 Bit

5 Bit

16 Bit

32 Bit

Nemesis C (TU Berlin) [114, 198]

96

16

32 Bit

4 Bit

1 Bit

16 Bit

PowerPC 970 (IBM) [67]

32

32

64 Bit

5 Bit

16 Bit

32 Bit

UltraSPARC III Cu (Sun) [172]

160

32

64 Bit

5 Bit

13 Bit

32 Bit

a. Der ARM7TDMI verfügt über einen alternativen, eingeschränkten Befehlssatz mit 16 Bit

breiten Befehlen, die sog. thumb instructions. Sie sind hier nicht berücksichtigt.

b. Der Prozessor wird benutzt, um Pentiumbefehle nach einer sog. dynamischen Binärüberset-

zung zu verarbeiten. Der Befehlssatz, mit dem der Prozessor tatsächlich arbeitet, ist nicht of-

fengelegt.

c. Die Angabe bezieht sich auf die meisten arithmetisch-logischen Operationen. Einige Opera-

tionen, z.B. die Addition, kann nämlich mehr als 8 Bit breite unmittelbare Operanden verar-

beiten (14 oder 22 Bit).

d. Bei diesen Prozessoren handelt es sich um VLIW-Prozessoren, die mit einem Befehl mehrere

darin codierte Operationen parallel verarbeiten können. Die Angaben beziehen sich auf eine

einzelne Operation inklusive der zugehörigen Adressen.

Zur Vermeidung der hier notwendigen Initialisierung erlauben es einige Prozessoren

nichtkommutative Operationen mit vertauschten Operanden auszuführen. So ver-

fügt der ARM7TDMI von ARM ltd. z.B. über den Befehl rsb (

reverse subtract

), mit

dem die Operation 1

-x

in einem Schritt als

-x

+1 ausgeführt werden kann, wobei

die unmittelbare Eins direkt als zweiter Operand im Befehl codierbar ist [10]. Im

Prinzip wird die herkömmliche Subtraktion mit einem unmittelbaren Wert nun nicht

mehr benötigt, da sie durch Addition der negierten Konstante nachgebildet werden

Search WWH ::

Custom Search