Information Technology Reference

In-Depth Information

der Hard- und Software, das Ausführen privilegierter Aktionen, die Emulation kom-

plexer, in Hardware nicht verfügbarer Befehle, die Speicherverwaltung, das Wech-

seln von Kontexten und die Verwaltung von Ausnahmen und Unterbrechungen

genannt [25]. Das Handbuch zur Prozessorarchitektur IA-64 von Intel bzw. HP führt

zusätzlich die Bearbeitung von Fehlern, das Powermanagement und das Testen von

Hardware auf [74]. Mit der Nemesis-Architektur der TU Berlin wird schließlich

noch von Ausnahme- und Unterbrechungsprogrammen abstrahiert (siehe Abschnitt

4.2.7) [114].

Beispiel 4.3.

Abstraktion durch PAL-Funktionen

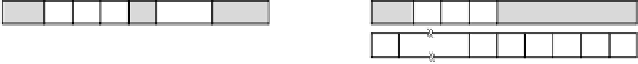

. Bild 4.17a zeigt ein Statusregister sr, wie es

ähnlich in Prozessoren mit MC68000- oder SPARC-Architektur realisiert ist [120, 162]. Neben

beliebigen Statusbits x, y und z ist insbesondere ein Feld irq vorhanden, in dem sich eine

Unterbre-

chungspriorität

eingetragen lässt. Dabei gilt, dass Unterbrechungsanforderungen nur dann akzep-

tiert werden, wenn die jeweiligen Prioritäten größer als der in irq codierte Wert ist. Die in Bild

4.17a ebenfalls dargestellte Befehlsfolge zeigt, wie sich die Unterbrechungspriorität 2 setzen lässt.

Zunächst wird der Inhalt des Statusregisters, wegen der darin codierten restlichen Einstellungen

gelesen (Zeile 1), der neue Prioritätswert eingetragen (Zeile 2 und 3) und schließlich das Ergebnis

in das Statusregister zurückgeschrieben (Zeile 4).

Ein Vorteil der Maskierung von Unterbrechungen anhand ihrer Prioritäten ist, dass nur wenige Bits

benötigt werden, um im Prinzip beliebig viele Unterbrechungsquellen verwalten zu können. Nach-

teilig ist jedoch, dass den Unterbrechungsquellen feste Prioritäten zugeordnet sein müssen und ein

individuelles Freischalten nicht möglich ist. Prozessoren einer zweiten Generation könnte man des-

halb in einer Weise realisieren, bei der statt einer Unterbrechungspriorität ein

Maskenregister

msk,

wie in Bild 4.17b angedeutet, vorgesehen wird. Dadurch ist es nämlich möglich, Unterbrechungen

durch Setzen eines einzelnen Bits individuell zu deaktivieren.

31

10

8

0

31

0

sr

x

y

z

irq

sr

x

y

z

msk

i

31

i

5

i

4

i

3

i

2

i

1

i

0

1: rd

r1 = sr

1: rd

r1 = msk

2: and

r1 = r1, 0x700

2: and

r1 = r1, 0xfff

3: wr

msk = r1

3: or

r1 = r1, 0x200

a

b

4: wr

sr = r1

Bild 4.17.

Techniken zum Maskieren von Unterbrechungsanforderungen.

a

anhand der Priorität des

Unterbrechungssignals.

b

Anhand einzelner Maskenbits

Allerdings müssen als Folge die existierenden Programme z.B. zur Verwaltung von Unterbre-

chungsanforderungen portiert werden, und zwar, indem man die in Bild 4.17a dargestellte Befehls-

folge durch die in Bild 4.17b dargestellte Befehlsfolge substituiert (der Einfachheit halber sei ange-

nommen, dass die zu maskierenden Unterbrechungen der Prioritäten 0 bis 2 den Unterbrechungs-

quellen i

0

bis i

11

entsprechen). Dieser Schritt lässt vermeiden, wenn das Setzen der Unterbre-

chungspriorität nicht direkt, sondern mit Hilfe einer PAL-Funktion geschieht, die vom Prozessor

abhängig eine der beiden in Bild 4.17 dargestellten Befehlsfolgen kapselt.

Selbstverständlich muss in Kauf genommen werden, dass ein individuelles Maskieren von Unter-

brechungen zunächst nicht möglich ist, auch wenn ein Prozessor Verwendung findet, der das Mas-

kenregister msk implementiert. Durch kompatible Erweiterung der Prozessorabstraktionsschicht

lässt sich dieser Nachteil jedoch in zukünftigen Anwendungen beheben. Beachtenswert ist, dass

eine Modifikation, wie sie hier angedeutet ist, oft noch weiterreichende Folgen hat, als man

zunächst vermuten mag. So kann es erforderlich sein, bei einem

Kontextwechsel

den Inhalt des Sta-

tusregisters inklusive der Unterbrechungspriorität bzw. -maske zu sichern. In der einen, hier ange-

Search WWH ::

Custom Search